BACHELOR DEGREE IN TELECOMMUNICATIONS, Digital Circuits and Systems (CSD), March 21, 2017. Grades will be available on March 25. Questions about the exam: Instructors' office time. It is mandatory to explain all the steps that you follow to solve each exercise in order to get grades. A student interview about the submitted work can also be requested.

## **Individual Test 1**

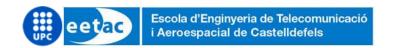

The entity represented in Fig. 1a is an electronic dice decoder, a combinational block for adapting the binary numbers from 1 to 6 to a 7-LED display that has the typical layout shown in Fig. 1b. Codes "000" and "111" don't care.

Fig. 1 Circuit for driving an electronic dice decoder. A version of this circuit runs here in Proteus.

- 1. Deduce the decoder truth table of all the outputs  $Li = f(E_L, X2, X1, X0)$ .

- 2. Describe the algebraic expression of L3 as a product of maxterms.

- 3. Describe the algebraic expression of **L1** as a sum of minterms.

- 4. Express the output **L6** using only NAND.

- 5. Implement the output L7 using the method of multiplexers and a MUX4 component.

- 6. Draw a behavioural flow chart and translate it to a VHDL file for the *dice\_decoder*.

- 7. Using the <u>method of decoders</u> and a *Decoder\_3\_8* component, draw a schematic for the *dice\_decoder* and write it in VHDL file. How many files are required?

- 8. If the following table in Fig. 2 represents the output from Minilog when inputting the *dice\_decoder* <u>truth</u> table and simplifying by **PoS**, write down the equations for the outputs **L4** and **L6**.

| E            |         |

|--------------|---------|

| XXX          | LLLLLLL |

| <u>L</u> 210 | 1234567 |

| ======       | ======  |

| -11-         | 11      |

| 1            | 1       |

| 1-           | .11     |

| -1           | 1111.   |

| 0            | 1111111 |

Fig. 2 Output table format from Minilog.exe.

a) Addition: (+116) + (-33)

b) Subtraction: (-33) - (+100)

c) Subtraction: (-100) - (-33)

d) Addition: (-125) + (+125)

Fig. 3 Add and subtract in 8-bit 2C convention.

- 9. Solve the arithmetic operations in Fig. 3 using 8-bit 2C (two's complement) number representation. Indicate when there is an overflow situation (OV flag). Which is the valid range of the operands and operations?

- 10. Propose a circuit structure able to perform the 8-bit 2C operations in 9).