# Problems on digital circuits and systems (CSD)

This is the former CSD problem collection. Not currently updated, kept only as a reference for old digsys links.

The idea is to transfer and rewrite problems from P1 to P12 to digsys web pages as sample projects.

Francesc J. Robert Josep Jordana

### **Contents**

| Prefac                 | ce                                                                   | .11 |  |  |  |

|------------------------|----------------------------------------------------------------------|-----|--|--|--|

| Combinational circuits |                                                                      |     |  |  |  |

| P1 Logi                | c gates and Boolean algebra                                          | 16  |  |  |  |

|                        | ves                                                                  |     |  |  |  |

| 1.1                    | Circuit analysis, truth tables and maxterms and minterms             | 17  |  |  |  |

| 1.2                    | Design Circuit_C using minimised equations                           | 20  |  |  |  |

| 1.3                    | Design Circuit_K using minimised equations                           | 21  |  |  |  |

| 1.4                    | Circuits using only NOR or only NAND                                 | 22  |  |  |  |

| 1.5                    | Circuits using only NOR or only NAND                                 | 23  |  |  |  |

| 1.6                    | Logic equations (PoS, SoP, maxterms, minterms)                       | 23  |  |  |  |

| P2 Stan                | dard logic circuits and flat VHDL design                             | 25  |  |  |  |

| Objecti                | ves                                                                  | 25  |  |  |  |

| 2.1                    | Using VHDL EDA tools for synthesis and simulation                    | 26  |  |  |  |

| 2.2                    | Designing a MUX_8 using several architectures                        | 27  |  |  |  |

| 2.3                    | Designing a HEX_7SEG_decoder                                         | 28  |  |  |  |

| 2.4                    | Designing a 10-line to 4-line priority encoder                       | 29  |  |  |  |

| 2.5                    | Designing an 8-line to 3-line priority encoder                       | 32  |  |  |  |

| 2.6                    | A digital wind direction meter                                       | 34  |  |  |  |

| P3 Arith               | nmetic circuits: adders, multipliers, comparators, etc. and VHDL     |     |  |  |  |

| hierarcl               | hical design (plan C2)                                               | 39  |  |  |  |

| Objecti                | ves                                                                  | 39  |  |  |  |

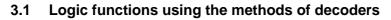

| 3.1                    | Logic functions using the methods of decoders                        | 40  |  |  |  |

| 3.2                    | Logic functions using the method of multiplexers                     | 41  |  |  |  |

| 3.3                    | Design a 1-bit full adder (flat)                                     | 42  |  |  |  |

| 3.4                    | Design a 1-bit full adder (structural)                               | 43  |  |  |  |

| 3.5                    | Design a 1-bit comparator                                            | 44  |  |  |  |

| 3.6                    | Designing a MUX_8 using a multiple-file structure                    | 45  |  |  |  |

| 3.7                    | 4-bit ripple adder                                                   |     |  |  |  |

| 3.8                    | 8-bit binary adder using 4-bit carry-look ahead adders               | 47  |  |  |  |

| 3.9                    | Designing a 6-bit comparator using VHDL                              | 48  |  |  |  |

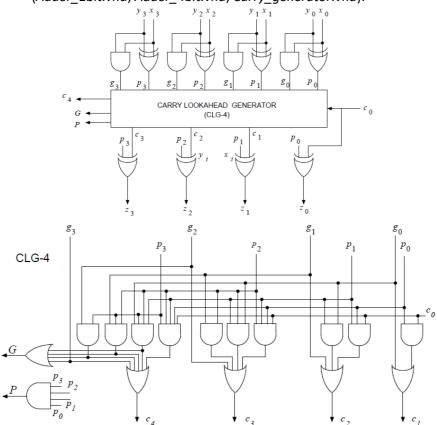

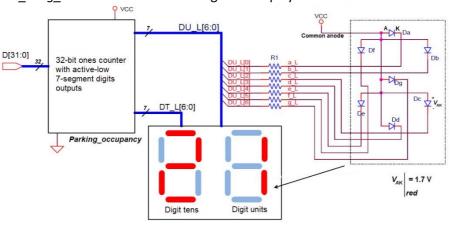

| 3.10                   | Counting occupied parking slots (32-bit ones' counter)               |     |  |  |  |

| 3.11                   | 1-bit subtractor                                                     |     |  |  |  |

| P4 Arith               | nmetic circuits for 2C integer numbers and gate-level simulations fo | r   |  |  |  |

|                                                                                                                        | tives                                                                                                                                                                                                                                                                                                                                                                                                                                    | 53                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

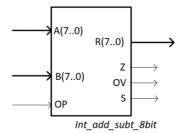

| 4.1                                                                                                                    | Addition and subtraction in two's complement                                                                                                                                                                                                                                                                                                                                                                                             | 54                                                                                                             |

| 4.2                                                                                                                    | Designing an 8-bit adder/subtractor for integer numbers                                                                                                                                                                                                                                                                                                                                                                                  | 55                                                                                                             |

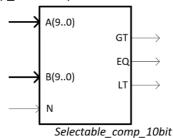

| 4.3                                                                                                                    | Designing a 10-bit comparator for radix-2 and 2C numbers                                                                                                                                                                                                                                                                                                                                                                                 | 56                                                                                                             |

| 4.4                                                                                                                    | Performing gate-level simulations and propagation time                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                |

| mea                                                                                                                    | asurements                                                                                                                                                                                                                                                                                                                                                                                                                               | 57                                                                                                             |

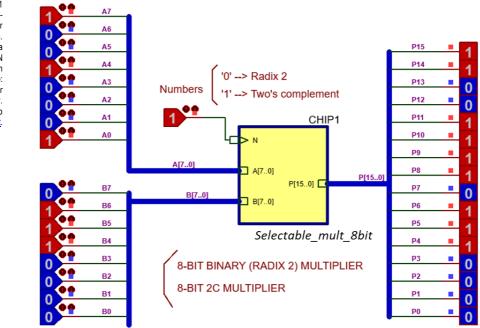

| 4.5                                                                                                                    | How to design an 8-bit multiplier for 2C integer numbers?                                                                                                                                                                                                                                                                                                                                                                                | 58                                                                                                             |

| Sequ                                                                                                                   | ential systems                                                                                                                                                                                                                                                                                                                                                                                                                           | 61                                                                                                             |

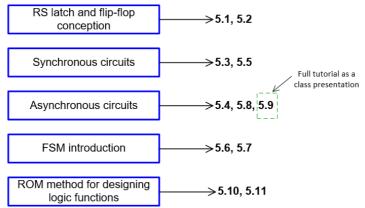

| P5 1-ł                                                                                                                 | it memory cells: latches and flip-flops                                                                                                                                                                                                                                                                                                                                                                                                  | 62                                                                                                             |

| Objec                                                                                                                  | tives                                                                                                                                                                                                                                                                                                                                                                                                                                    | 62                                                                                                             |

| 5.1                                                                                                                    | Designing and using an RS latch. Deducing an RS_FF                                                                                                                                                                                                                                                                                                                                                                                       | 63                                                                                                             |

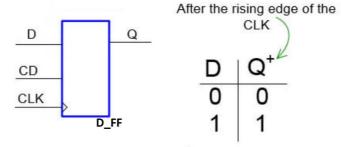

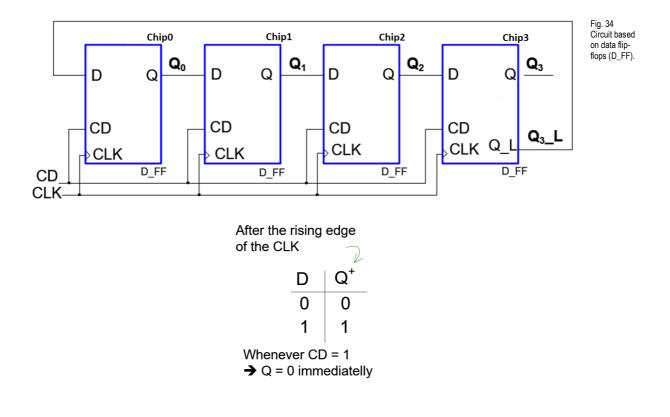

| 5.2                                                                                                                    | Data flip-flop (D_FF)                                                                                                                                                                                                                                                                                                                                                                                                                    | 64                                                                                                             |

| 5.3                                                                                                                    | Analysis of a synchronous circuit                                                                                                                                                                                                                                                                                                                                                                                                        | 65                                                                                                             |

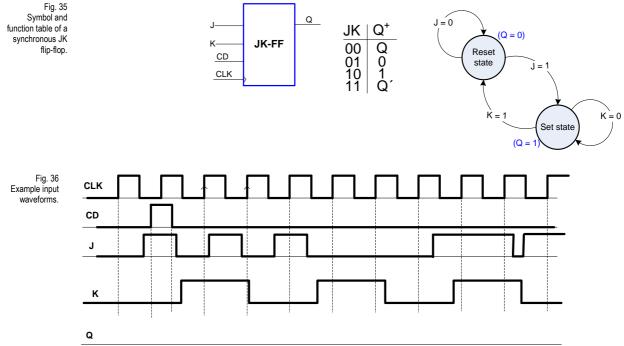

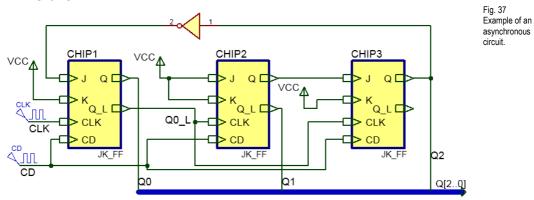

| 5.4                                                                                                                    | JK_FF and analysis of an asynchronous circuit                                                                                                                                                                                                                                                                                                                                                                                            | 66                                                                                                             |

| 5.5                                                                                                                    | Analysis of a synchronous circuit                                                                                                                                                                                                                                                                                                                                                                                                        | 69                                                                                                             |

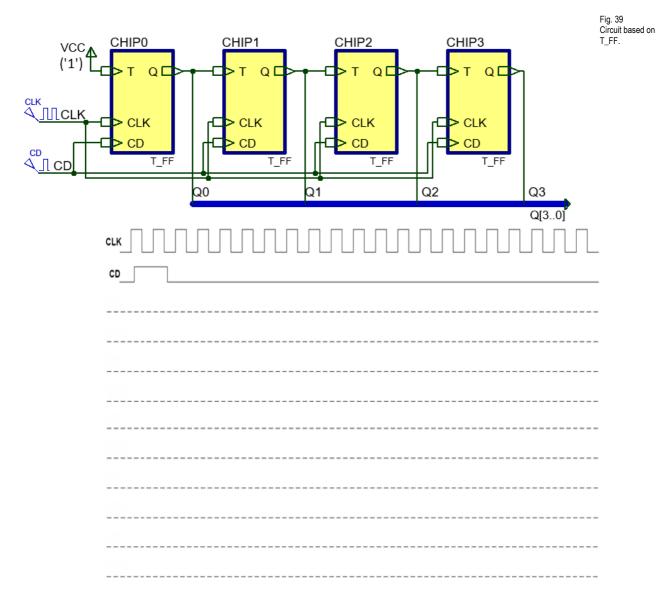

| 5.6                                                                                                                    | Design a toggle flip-flop (T_FF) using the FSM strategy                                                                                                                                                                                                                                                                                                                                                                                  | 70                                                                                                             |

| 5.7                                                                                                                    | Design a JK flip-flop using the FSM strategy                                                                                                                                                                                                                                                                                                                                                                                             | 71                                                                                                             |

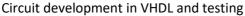

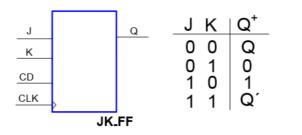

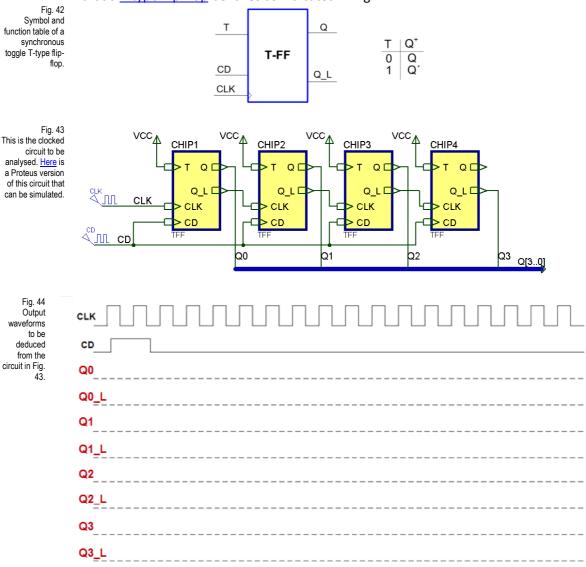

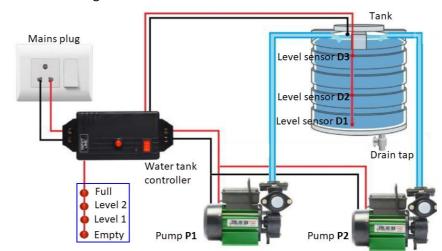

| 5.8                                                                                                                    | Analysis of an asynchronous counter (type 7493)                                                                                                                                                                                                                                                                                                                                                                                          | 72                                                                                                             |

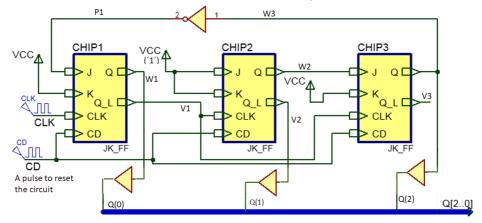

| 5.9                                                                                                                    | Analysis of an asynchronous circuit based on T_FF                                                                                                                                                                                                                                                                                                                                                                                        | 73                                                                                                             |

| 5.10                                                                                                                   | D Design a combinational circuit using the method of ROM                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                |

| me                                                                                                                     | nories                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                |

|                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                |

| 5.1                                                                                                                    | L Design a HEX_7seg using the method of ROM memories                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                |

| -                                                                                                                      | L Design a HEX_7seg using the method of ROM memories<br>ite State Machines (FSM)                                                                                                                                                                                                                                                                                                                                                         | 75                                                                                                             |

| P6 Fin                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                          | 75<br>76                                                                                                       |

| P6 Fin                                                                                                                 | ite State Machines (FSM)                                                                                                                                                                                                                                                                                                                                                                                                                 | 75<br>76<br>76                                                                                                 |

| P6 Fin<br>Objec                                                                                                        | ite State Machines (FSM)                                                                                                                                                                                                                                                                                                                                                                                                                 | 75<br>76<br>76<br>77                                                                                           |

| P6 Fin<br>Objec<br>6.1                                                                                                 | ite State Machines (FSM)<br>tives<br>Controlling the classroom luminaires                                                                                                                                                                                                                                                                                                                                                                | 75<br>76<br>76<br>77<br>78                                                                                     |

| P6 Fin<br>Objec<br>6.1<br>6.2                                                                                          | ite State Machines (FSM)<br>tives<br>Controlling the classroom luminaires<br>Invent a bicycle torch                                                                                                                                                                                                                                                                                                                                      | 75<br>76<br>76<br>76<br>78<br>78<br>78                                                                         |

| P6 Fin<br>Objec<br>6.1<br>6.2<br>6.3                                                                                   | ite State Machines (FSM)<br>tives<br>Controlling the classroom luminaires<br>Invent a bicycle torch<br>Debouncing circuit                                                                                                                                                                                                                                                                                                                | 75<br>76<br>76<br>77<br>78<br>78<br>79                                                                         |

| P6 Fin<br>Objec<br>6.1<br>6.2<br>6.3<br>6.4                                                                            | ite State Machines (FSM)<br>tives<br>Controlling the classroom luminaires<br>Invent a bicycle torch<br>Debouncing circuit<br>16-key matrix encoder                                                                                                                                                                                                                                                                                       | 75<br>76<br>76<br>77<br>78<br>78<br>79<br>80                                                                   |

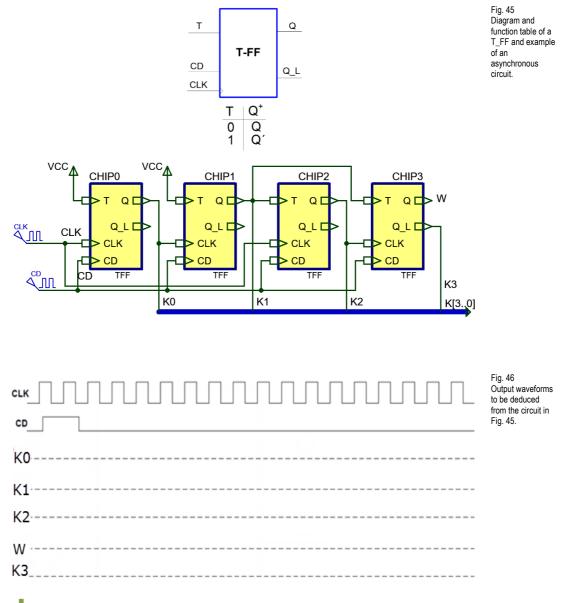

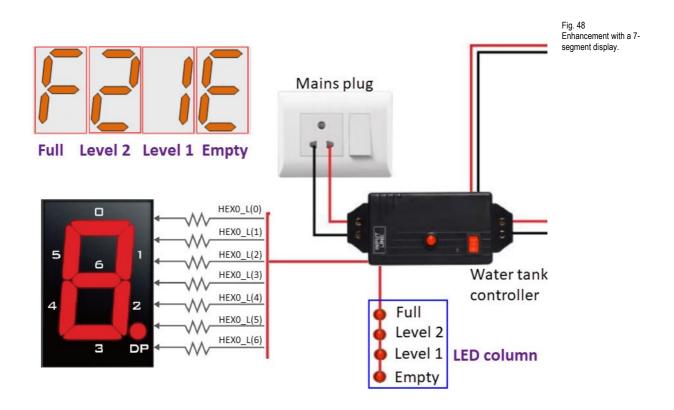

| P6 Fin<br>Objec<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5                                                                     | ite State Machines (FSM)<br>tives<br>Controlling the classroom luminaires<br>Invent a bicycle torch<br>Debouncing circuit<br>16-key matrix encoder<br>Water tank controller                                                                                                                                                                                                                                                              | 75<br>76<br>76<br>77<br>78<br>78<br>78<br>                                                                     |

| P6 Fin<br>Objec<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6                                                              | ite State Machines (FSM)<br>tives<br>Controlling the classroom luminaires<br>Invent a bicycle torch<br>Debouncing circuit<br>16-key matrix encoder<br>Water tank controller<br>Traffic light controller                                                                                                                                                                                                                                  | 75<br>76<br>76<br>78<br>78<br>78<br>78<br>79<br>80<br>82<br>83                                                 |

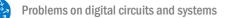

| P6 Fin<br>Objec<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>P7 Sta                                      | ite State Machines (FSM)<br>tives<br>Controlling the classroom luminaires<br>Invent a bicycle torch<br>Debouncing circuit<br>16-key matrix encoder<br>Water tank controller<br>Traffic light controller<br>Stepper motor controller<br>7-segment digit sequencer                                                                                                                                                                         | 75<br>76<br>76<br>78<br>78<br>78<br>78<br>78<br>78<br>                                                         |

| P6 Fin<br>Objec<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>P7 Sta                                      | ite State Machines (FSM)<br>tives.<br>Controlling the classroom luminaires<br>Invent a bicycle torch<br>Debouncing circuit<br>16-key matrix encoder<br>Water tank controller<br>Traffic light controller<br>Stepper motor controller<br>7-segment digit sequencer<br>indard counters and registers                                                                                                                                       | 75<br>76<br>76<br>78<br>78<br>78<br>78<br>79<br>80<br>82<br>84<br>84<br>86<br>86                               |

| P6 Fin<br>Objec<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>P7 Sta<br>Objec<br>7.1                      | ite State Machines (FSM)<br>tives<br>Controlling the classroom luminaires<br>Invent a bicycle torch<br>Debouncing circuit<br>16-key matrix encoder<br>Water tank controller<br>Traffic light controller<br>Stepper motor controller<br>7-segment digit sequencer<br>indard counters and registers<br>1-digit BCD counter (flat)                                                                                                          | 75<br>76<br>76<br>78<br>78<br>78<br>79<br>80<br>82<br>83<br>84<br>84<br>86<br>87                               |

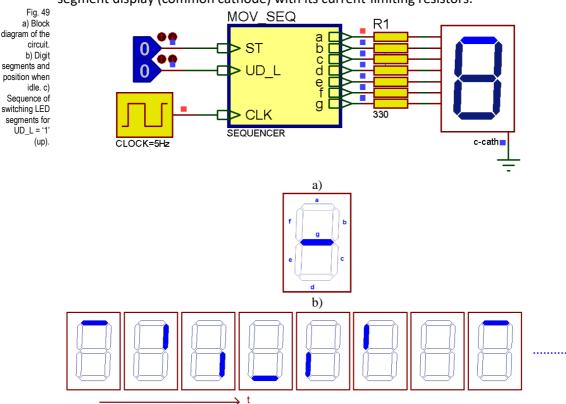

| P6 Fin<br>Objec<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>P7 Sta<br>Objec<br>7.1<br>7.2               | ite State Machines (FSM)<br>tives<br>Controlling the classroom luminaires<br>Invent a bicycle torch<br>Debouncing circuit<br>16-key matrix encoder<br>Water tank controller<br>Traffic light controller<br>Stepper motor controller<br>7-segment digit sequencer<br>indard counters and registers<br>tives<br>1-digit BCD counter (flat)<br>Synchronous universal 4-bit binary counter                                                   | 75<br>76<br>76<br>78<br>78<br>78<br>78<br>78<br>78<br>78<br>78<br>78<br>78<br>80<br>81<br>86<br>87<br>88       |

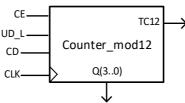

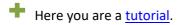

| P6 Fin<br>Objec<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>P7 Sta<br>Objec<br>7.1<br>7.2<br>7.3        | ite State Machines (FSM)<br>tives.<br>Controlling the classroom luminaires<br>Invent a bicycle torch<br>Debouncing circuit<br>16-key matrix encoder<br>Water tank controller<br>Traffic light controller<br>Stepper motor controller<br>7-segment digit sequencer<br>indard counters and registers<br>tives.<br>1-digit BCD counter (flat)<br>Synchronous universal 4-bit binary counter<br>Synchronous modulo 12 counter                | 75<br>76<br>76<br>78<br>78<br>78<br>78<br>78<br>78<br>78<br>78<br>78<br>                                       |

| P6 Fin<br>Objec<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>P7 Sta<br>Objec<br>7.1<br>7.2<br>7.3<br>7.4 | ite State Machines (FSM)<br>tives<br>Controlling the classroom luminaires<br>Invent a bicycle torch<br>Debouncing circuit<br>16-key matrix encoder<br>Water tank controller<br>Traffic light controller<br>Stepper motor controller<br>7-segment digit sequencer<br>indard counters and registers<br>tives<br>1-digit BCD counter (flat)<br>Synchronous universal 4-bit binary counter<br>Synchronous modulo 12 counter<br>Data register | 75<br>76<br>76<br>78<br>78<br>78<br>79<br>79<br>80<br>82<br>83<br>84<br>86<br>86<br>87<br>88<br>               |

| P6 Fin<br>Objec<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>P7 Sta<br>Objec<br>7.1<br>7.2<br>7.3        | ite State Machines (FSM)<br>tives.<br>Controlling the classroom luminaires<br>Invent a bicycle torch<br>Debouncing circuit<br>16-key matrix encoder<br>Water tank controller<br>Traffic light controller<br>Stepper motor controller<br>7-segment digit sequencer<br>indard counters and registers<br>tives.<br>1-digit BCD counter (flat)<br>Synchronous universal 4-bit binary counter<br>Synchronous modulo 12 counter                | 75<br>76<br>76<br>78<br>78<br>78<br>79<br>80<br>82<br>83<br>84<br>84<br>86<br>86<br>87<br>88<br>90<br>91<br>92 |

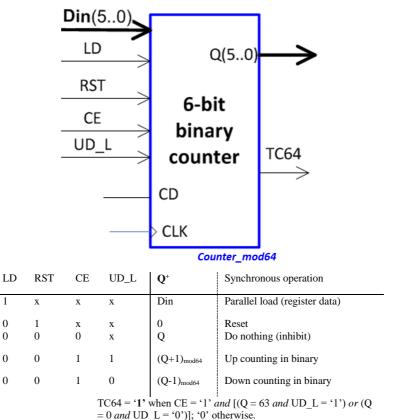

| 7.7     | 6-bit binary universal counter                                        | 95    |

|---------|-----------------------------------------------------------------------|-------|

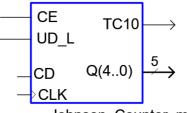

| 7.8     | Johnson counter                                                       | 97    |

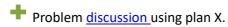

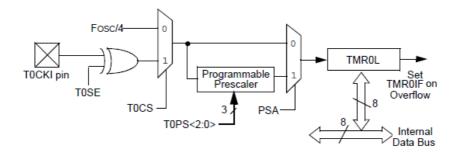

| 7.9     | PIC18F4520 TMR2 prescaler design                                      | 99    |

| P8 Ded  | icated processors and advanced circuits                               |       |

|         | ves                                                                   |       |

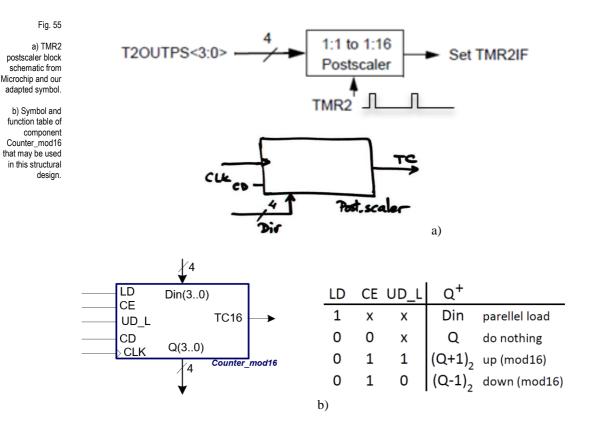

| 8.1     | Generation of CLK signals                                             |       |

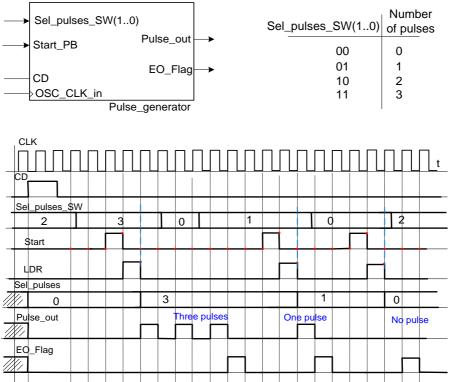

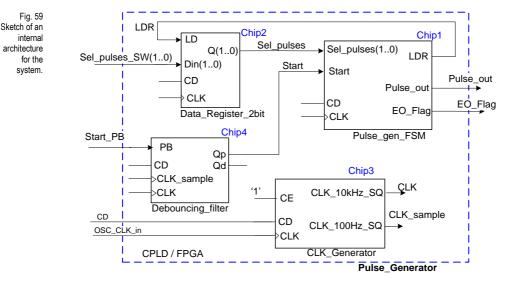

| 8.2     | Pulse generator                                                       |       |

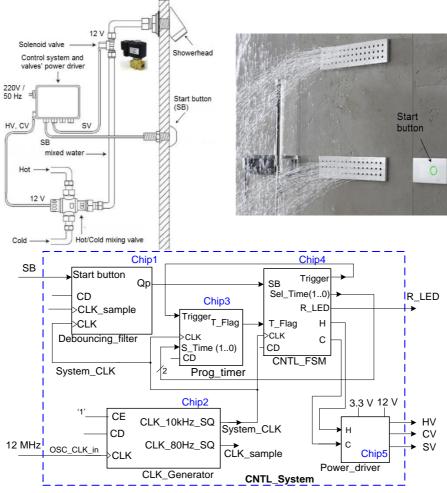

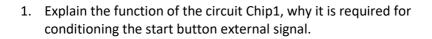

| 8.3     | Designing an industrial application                                   | 105   |

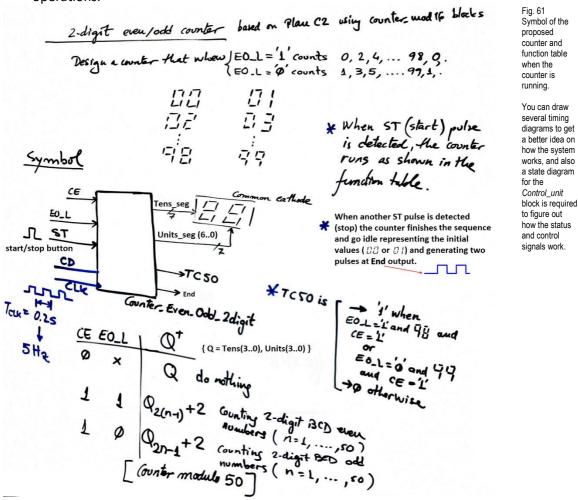

| 8.4     | Design a 2-digit even/odd counter with start/stop button              |       |

| 8.5     | Synchronous serial adder                                              |       |

| 8.6     | Timer MMSS                                                            | 109   |

| 8.7     | Synchronous serial multiplier                                         | 110   |

| 8.8     | Serial transmitter and receiver (USART)                               | 111   |

| 8.9     | Steeping motor control based on a dedicated processor                 | 112   |

| Micro   | controller applications                                               | 11/   |

| IVIICIC |                                                                       | 114   |

| P9 Basi | c theory on microcontrollers ( $\mu$ C) and basic digital I/O interfa | ce114 |

| Objecti | ves                                                                   |       |

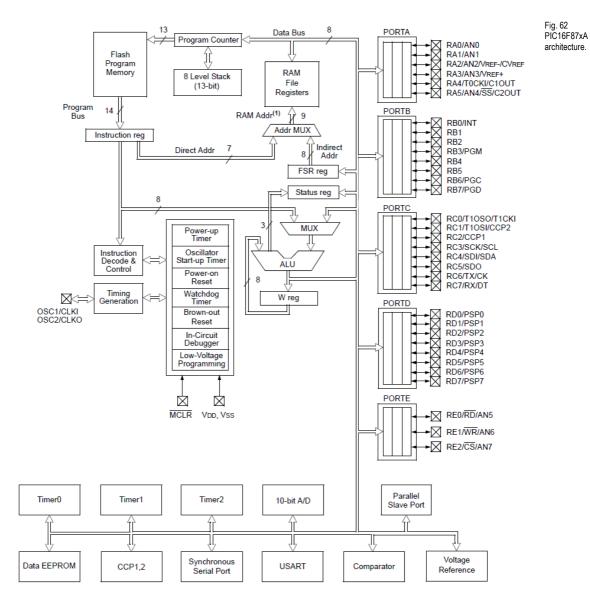

| 9.1     | The microcontroller PIC16F                                            | 115   |

| 9.2     | Invent a Dual_MUX4 based on a µC                                      | 118   |

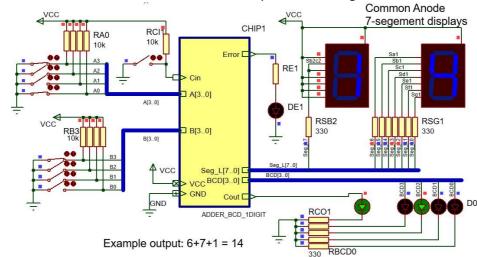

| 9.3     | 1-digit BCD adder                                                     | 119   |

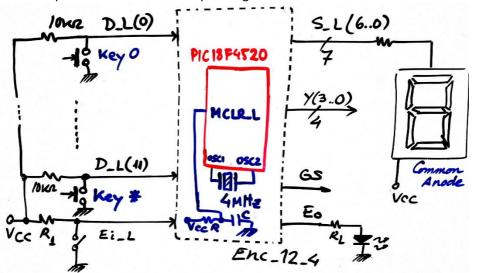

| 9.4     | 12-to-4 encoder                                                       | 121   |

| P10 Pro | ograming FSM in C style. Events detection using interrupts            | 123   |

| Objecti | ves                                                                   | 123   |

| 10.1    | 1-digit BCD counter                                                   | 124   |

| 10.2    | Binary counter modulo 256                                             | 124   |

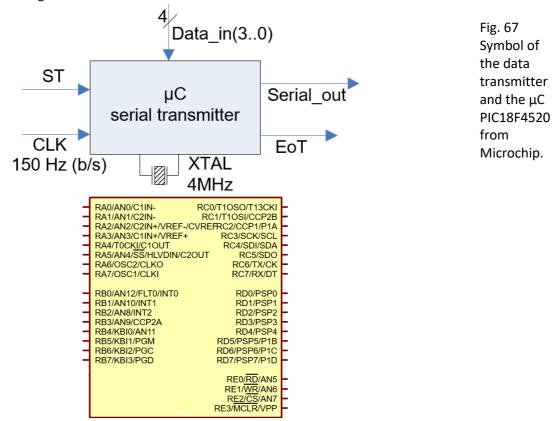

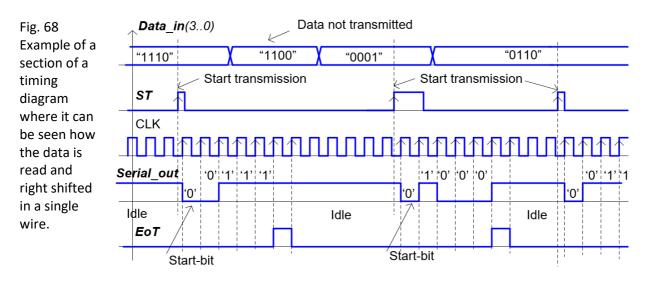

| 10.3    | 4-bit serial data transmitter                                         | 125   |

| 10.4    | 5-bit Johnson counter                                                 | 127   |

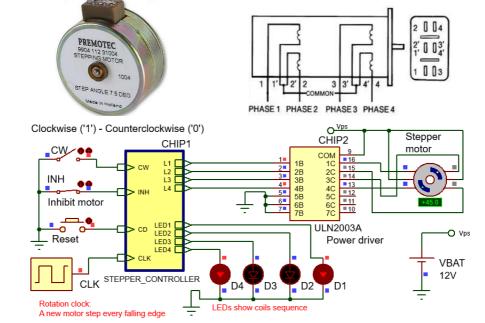

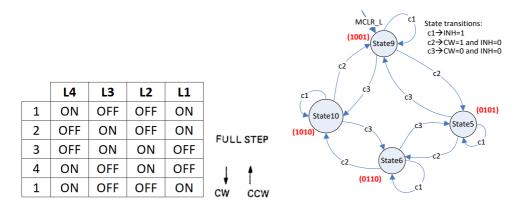

| 10.5    | Stepper motor controller                                              | 128   |

| P11 Pe  | ripherals: LCD display                                                |       |

|         | ves                                                                   |       |

| -       | LCD display using ASCII messages and static data                      |       |

| 11.2    | LCD display using dynamic data                                        |       |

| 11.3    | Interfacing an I2C display                                            |       |

| D12 Do  |                                                                       |       |

|         | ripherals and complex applications                                    |       |

| 12.1    | ves<br>Industrial application                                         |       |

| 12.1    |                                                                       |       |

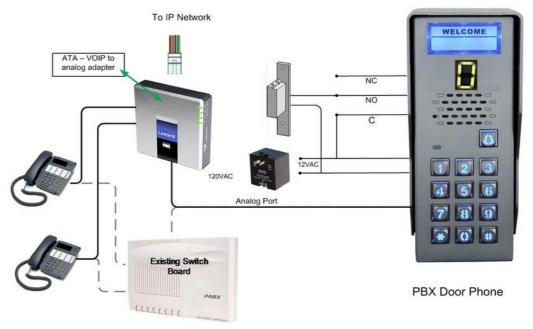

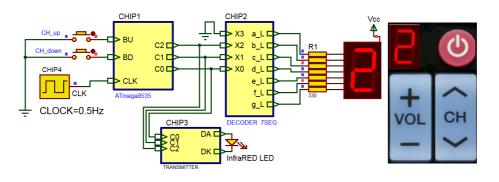

| 12.2    | Simple remote control                                                 |       |

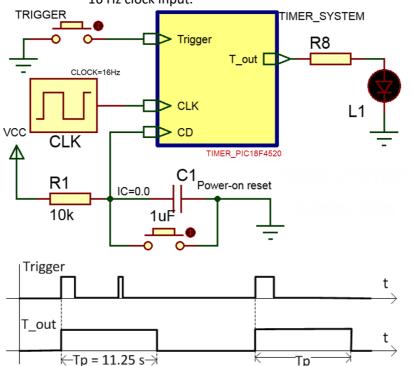

| 12.3    | Non-retriggerable timer<br>Timers. PWM generation                     |       |

| 12.4    | ווווכוס. ד אואו צבוובו מנוטוו                                         |       |

| 12.5        | Temperature measurement using timers           | 141 |

|-------------|------------------------------------------------|-----|

| 12.6        | Temperature measurement using A/D converters . | 141 |

| Bibliogr    | aphy and internet links                        | 143 |

| Bibliograp  | bhy                                            |     |

| Internet li | inks                                           |     |

### Preface

This publication is the initial draft of a collection of problems and exercises from the former Digital Electronics (ED) and Digital Electronic Systems (SED) subjects and from past editions of the Digital Circuits and Systems (CSD) course for which this learning resource has been created. The publication, which is now under construction, will contain reviewed versions of design exercises from the three chapters in which CSD is organised: combinational circuits, finite state machines (FSM) and dedicated processors, and microcontrollers.

The aim of this publication is to help students to develop the following telecommunications engineering competencies associated with the <u>CSD</u> <u>course</u>:

- CE 14 TELECOM. A capacity for the analysis and design of synchronous and asynchronous combinatorial and sequential circuits, and the ability to use microprocessors and integrated circuits.

- CE 15 TELECOM. Knowledge of and the ability to apply the fundamentals of hardware description languages. (CIN/352/2009, BOE 20/2/2009)

- PROJECT MANAGEMENT Level 1: The ability to use project management tools to carry out the stages of a project set by the professor.

- EFFICIENT USE OF EQUIPMENT AND INSTRUMENTS Level 1: The ability to use the instruments, equipment and software of the laboratories for general or basic use and to carry out experiments and practicals and analyse the results.

- INDEPENDENT LEARNING Level 1. The ability to complete tasks in the time allotted, using the suggested materials and following the guidelines set by the professor.

- EFFECTIVE ORAL AND WRITTEN COMMUNICATION Level 1. The ability to complete tasks in the time allotted, using the suggested materials and following the guidelines set by the professor. The ability

to plan oral presentations, correctly reply to questions and write basic texts without spelling and grammar mistakes.

- TEAMWORK Level 1. The ability to take an active role in group work, which includes identifying specific goals, determining collective and individual responsibilities and reaching a consensus on the most suitable approach to adopt for each problem.

- FOREIGN LANGUAGE. Knowledge of a foreign language, preferably English, at an oral and written level that is consistent with what is required of students on each degree.

We would appreciate your comments on this list of projects, so that we can enhance the process of finding errors and making improvements. The table of contents is structured following the course <u>web page</u>.

Course organisation and basic learning goals

- Use your official UPC email address to communicate with your instructors for these reasons [8].

- Use and manage an e-mail client like Thunderbird [9] or Outlook.

- Use a SMB disk like your mapped "L" to carry out projects and assignments on school premises.

- Discuss the five elements required to achieve effective <u>cooperative</u> <u>learning</u>: positive interdependence; face-to-face interaction, individual accountability and personal responsibility, use of interpersonal and small-group skills and group processing or reflection.

- Analyse and manage your individual and group study time. Be aware that 6 ECTS are equivalent to 150 hours of study time.

- Produce quality written solutions for your projects using pen-andpaper. Then (optionally) use this <u>template</u> to complete and save the solutions in electronic format. Generally, project solutions consist of specifications, plan, development, test, report and, in some selected exercises, prototyping.

- (Optional) Use <u>Google sites</u> or a similar application to build your cooperative group <u>ePortfolio</u> and publish your projects, results and reflection.

## **Combinational circuits**

#### P1 Logic gates and Boolean algebra

#### Objectives

After studying the content of these projects, you will be able to:

- Use and explain the functionality of logic gates AND, NAND, OR, NOR, XOR, NXOR and NOT.

- Find datasheets of small and medium scale of integration (SSI and MSI) integrated circuits.

- Analyse a logic circuit built using logic gates (deduce its truth table).

- Explain and relate the following concepts for designing a logic circuit: truth table, canonical algebraic equations: minterms and maxterms, Boolean algebra and logic functions, minimisation: SoP (sum of products) and PoS (product of sums).

- Simplify or minimise logic functions using software like *Minilog.exe*.

- Use the application <u>WolframAlpha</u> to verify logic equations and determine the truth table of a combinational circuit.

- Use the <u>HADES</u> JAVA-based platform or <u>Deeds</u> to visualise and analyse the operation of digital circuits.

- Capture and simulate a schematic using the virtual laboratory software <u>Proteus-ISIS</u> or <u>MultiSim</u>.

- Search books and the internet to find information on the basics of VHDL language and explain the differences between VHDL design styles: structural and behavioural.

- Use the register transfer level (RTL) and technology schematic views to inspect the results of the synthesis process.

- Explain the basic technological details of an sPLD (22V10), CPLD or FPGA and how to program them to implement logic functions.

- Install computer-aided design (CAD) and electronic design automation (EDA) tools (<u>Lattice</u> Semiconductor ispLEVER Classic or Diamond, <u>Intel</u> Quartus II or Prime, and <u>Xilinx</u> ISE or Vivado), and run its design flow to implement VHDL projects for sPLD/CPLD/FPGA chips. Essentially the process involves VHDL source files, synthesis, functional simulation, pin assignment, gate-level simulation, target device programming and prototype verification.

- Simulate a logic circuit using EDA tools: ActiveHDL Lattice edition, ModelSim Intel edition or Xilinx ISim.

- Use sPLD/CPLD/FPGA development boards to prototype and verify the course projects.

#### 1.1 Circuit analysis, truth tables and maxterms and minterms

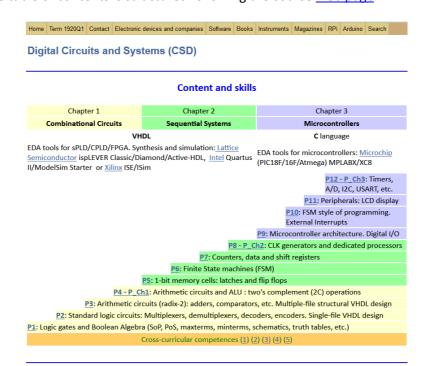

The aim of this exercise is firstly to analyse circuits A and B in Fig. 1 to obtain their truth tables  ${\sf P}$  =

https://digsys.upc.edu/csd/plan/lab1\_1/Plan\_Section\_A.jpgf(S1, S0, A, B); Q = f(S1, S0, A, B) and secondly to draw another equivalent circuit using the canonical logic equations (maxterms and minterms).

Let us establish a plan to solve this problem. Consider Circuit A and Circuit B as complete independent problems. First, solve Circuit A before continuing with

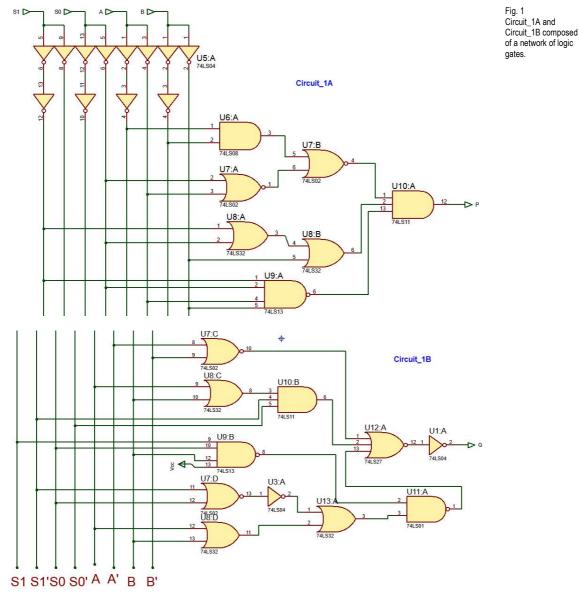

### Circuit B. Fig. 2 shows several ways to plan how to determine the truth table of a given simple combinational circuit composed of logic gates.

Phase A: Deduce and verify the circuit's truth table:

- 1. Method I. Draw the Circuit A, capture the schematics in Proteus and run simulations to obtain its truth table. There are up to 16 input combinations to complete the circuit truth table.

- Method II. Deduce the logic equation that exactly matches the circuit. The numerical engine <u>WolframAlpha</u> can be used to obtain the truth table by typing the equation directly and analysing the computer results.

- 3. Method III. Apply Boolean algebra to determine the truth table (which is equivalent to the sum of minterms or the product of maxterms). In this way, the SoP or PoS expressions will be obtained as a step towards the final truth table.

- 4. Method IV. Run a VHDL design flow using EDA tools (a single-file structural project, circuit synthesis and test bench functional simulation) to produce a circuit. Verify the circuit by means of a timing diagram from which to annotate a truth table that must be identical to that deduced using any of the three previous methods.

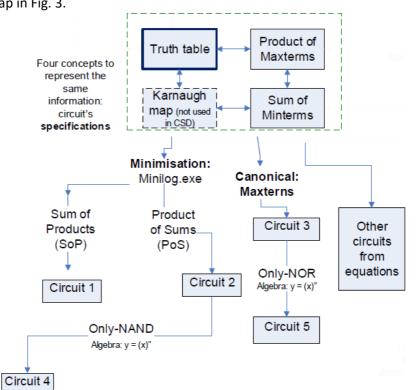

Fig. 3 Invention of circuits from the same initial

truth table.

**Phase B**: Invent several circuits from the given truth table, as shown in the map in Fig. 3.

- 5. Invent a canonical Circuit\_3 using the product of maxterms.

- 6. From Circuit\_3, obtain a new Circuit\_5 based on 2-input NOR gates.

- 7. Create a new Circuit\_2 by minimising the truth table and choosing PoS.

- 8. From Circuit\_2, derive a new Circuit\_4 based on 2-input NAND gates.

• Some ideas on the solution to the analysis problem can be found in this tutorial.

#### 1.2 Design Circuit\_C using minimised equations

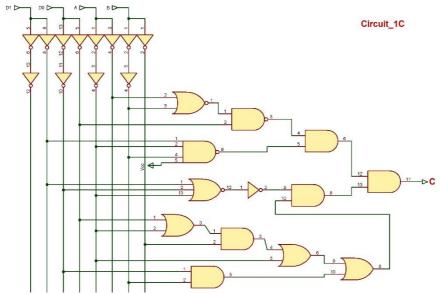

This exercise has two aims: first to analyse Circuit\_C in Fig. 4 to obtain its truth table, and second to draw an equivalent circuit using minimised equations like the sum of products (SoP) or the product of sums (PoS).

Fig. 4 Circuit\_C composed of a network of logic gates.

Let us follow the plan depicted in Fig. 2:

- Phase A: obtain the circuit's truth table by means of at least two of the four methods proposed, so that you can check that the truth table is correct.

- Phase B: invent another circuit using minimised equations.

Use an application like <u>Minilog</u> or <u>Logic Friday</u> to obtain minimised equations from a given truth table.

• Some ideas on the solution to the analysis problem can be found in this <u>tutorial</u>.

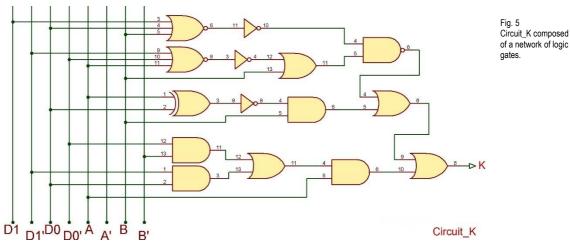

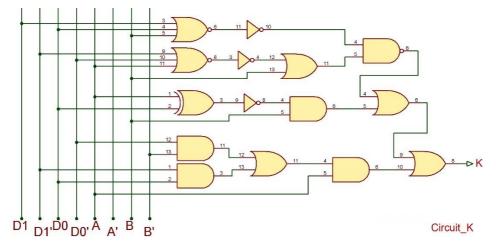

#### 1.3 Design Circuit\_K using minimised equations

This exercise has two aims, first to analyse Circuit\_K in Fig. 5 to obtain its truth table, and second to draw an equivalent circuit using minimised equations like the sum of products (SoP) or the product of sums (PoS).

Let us follow the plan shown in Fig. 2:

- Phase A: obtain the circuit's truth table by means of at least two of the four proposed methods, so that you can check the truth table is correct.

- Phase B: invent another circuit using minimised equations.

Use an application like <u>Minilog</u> or <u>Logic Friday</u> to obtain minimised equations from a given truth table.

• Some ideas on the solution of this analysis problem can be found in this <u>tutorial</u>.

#### 1.4 Circuits using only NOR or only NAND

Given the following Boolean expression:

$Q = f(x, y, z) = x \cdot y + y' \cdot z$

- a) Draw the circuit's truth table and symbol. Represent the circuit using only NAND logic gates.

- b) Express the output as a sum of minterms and a product of maxterms.

- c) With the equation obtained in *b*), represent the circuit using only-NOR logic gates.

- d) Calculate the maximum frequency of operation of this circuit if the propagation delay time t<sub>PHL</sub> and t<sub>PLH</sub> of a gate of this kind, for instance 74HCT technology is 21 ns.

- e) How would you use the VHDL simulator to verify the truth table of this digital circuit?

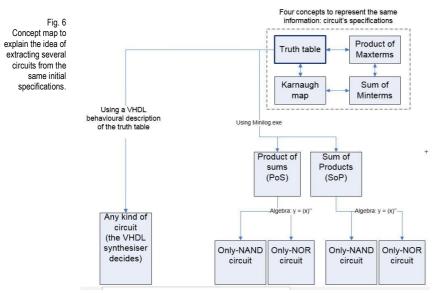

The representation in Fig. 6 is a map that can help to comprehend the concepts. Once you have deduced the circuit's truth table, you can produce several circuits that meet the same specifications.

#### 1.5 Circuits using only NOR or only NAND

Interpret the following table output format in Fig. 7 from Minilog.

- Draw the symbol of the circuit.

- First draw the logic circuit for the output  $\mathbf{A}_{\mathbf{L}} = f_1$  (D, C, B, A) using only NOR gates, and second modify the circuit so that all the gates are 2-input NOR.

- First draw the circuit for the output  $\mathbf{B}_{\mathbf{L}} = f_2$  (D, C, B, A) using only NAND gates, and second modify the circuit so that all the gates are 2-input NAND.

- How many maxterms and minterms contain the function  $E_L = f_3$  (D, C, B, A)?

| MINIMISATION RESULT STATISTICS                                                                             |                                                       |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|--|--|

| FOUND 28 ESSENTIAL FACTORS <b>IN</b><br><b>PRODUCT OF SUMS MODE</b>                                        | ABE<br>DCBA LLL                                       |  |  |  |  |  |

| MAXIMUM FANIN: 18<br>TOTAL LITERAL COUNT: 102<br>MAXIMUM FACTOR SIZE: 3<br>MAXIMUM OUTPUT FUNCTION SIZE: 6 | 011-   1<br>10-0   1<br>-1-1   111                    |  |  |  |  |  |

| Note: Remember that you must deduce the equivalent equations before you draw the circuits.                 | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |  |  |  |  |  |

|                                                                                                            | $\begin{array}{cccccccccccccccccccccccccccccccccccc$  |  |  |  |  |  |

Fig. 7 Output table format from a given circuit described in Minilog.

#### 1.6 Logic equations (PoS, SoP, maxterms, minterms)

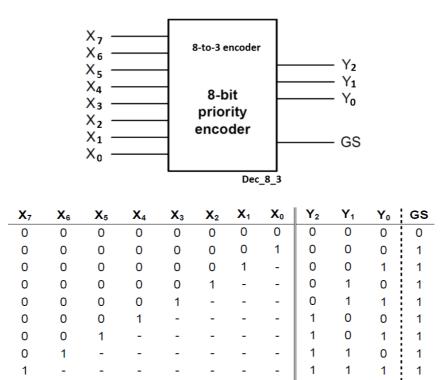

Fig. 8 shows the block diagram and the truth table of an 8-to-3 encoder (Enc\_8\_3), a typical next section example of standard circuit. When several inputs are active high at the same time, a binary code is generated of the highest priority signal. The symbol "-" means a "don't care" value that is represented other times by "x". **GS** goes high when any input is assessed, thus it can be used both as a flag to indicate that a key is pressed and for disambiguation of the code "000".

- Represent the output  $Y_2 = f(X_7...X_0)$  using a product of sums (PoS).

- Represent the output  $Y_1 = f(X_7...X_0)$  using a sum of products (SoP).

- Represent the output GS using maxterms. How many minterms will the function have?

- Write down the single-file (flat) VHDL code using either structural (plan A) or behavioural (plan B) style. Explain the differences between the two coding styles.

#### Objectives

After studying the content of these projects, you will be able to:

P2 Standard logic circuits and flat VHDL design

- Explain the specifications and characteristics of the standard combinational logic blocks: multiplexers (or data selectors), demultiplexers (or data distributors), decoders, encoders, hexadecimal to seven-segment LED displays adapters, code converters, etc.

Specifications include concepts like: symbol, truth table and functionality, internal design, expandability, and commercial chips of similar characteristics.

- Explain the functionality of the enable input that is available in most of these standard circuits.

- Explain the concepts of flat and hierarchical designs and implement simple projects in VHDL involving a single file (flat) using structural (plan A) or behavioural (plan B) approaches.

- Explain how to chain or expand such devices to implement a larger one, for instance, how to connect several MUX\_4 to obtain a MUX\_16.

- Implement standard circuits targeted at a given PLD (CPLD or FPGA) using VHDL and synthesis and simulation EDA tools. Explain the <u>VHDL</u> design flow.

- Find datasheets of classic logic circuits from different technologies.

- Explain how to interface switches to encoders.

- Explain how to interface LEDs and seven-segment display to decoder outputs.

#### 2.1 Using VHDL EDA tools for synthesis and simulation

Calculate the truth table of the circuit depicted in Fig. 9 using VHDL EDA tools. This is the analysis method #4 presented in  $\underline{P1}$  and a way to discover the concepts associated with the VHDL design flow.

- a) Understand the specifications and characteristics of VHDL synthesis and simulation tools.

- b) Organise a plan detailing the sequence of operations to reach the end of the problem successfully.

- c) Develop the solution.

- d) Test the truth table using other methods of circuit analysis such as those described in P1.

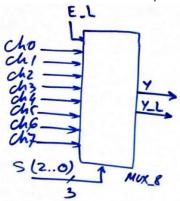

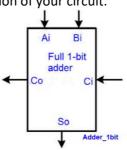

### 2.2 Designing a MUX\_8 using several architectures

The objective is to design the functionality of a MUX\_8 type 74HCT151 using VHDL synthesis and simulation EDA tools. The circuit MUX\_8 is simple and so it must be designed flat, which means a single VHDL file<sup>1</sup> is used to describe the complete architecture. Three plans are presented, so this problem is completely divided into three projects. Plan, develop and test them separately. This <u>reference</u> is a link to the VHDL design flow that states the entire sequence of operations required to succeed in the design.

- Plan A. Structural, using logic equations.

- Plan B. Behavioural, using the truth table or a high-level algorithm describing the chip's functionality.

- Plan C1. Invent a hierarchical schematic for MUX\_8 using smaller blocks of the same kind, for instance, MUX\_4 or MUX\_2.

Problem discussion.

<sup>1</sup> The plan C2 proposed in P3 can be used to design hierarchical structures using multiple-file projects, which enables the design of complex, large circuits.

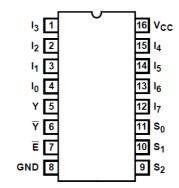

#### 2.3 Designing a HEX\_7SEG\_decoder

The objective is to design the functionality of a HEX\_7SEG\_decoder type 74LS47 using VHDL synthesis and simulation EDA tools. The symbol and truth table adapted from the datasheet are represented in Fig. 11. The design must be flat with all the architecture included in a single VHDL. Two plans are presented, so this problem is divided completely into two projects. Plan, develop and test them separately. This <u>reference</u> is a link to the VHDL design flow that states the entire sequence of operations required to succeed in the design.

Fig. 11 Hexadecimal to seven-segment decoder

• Plan A. Structural, using logic equations.

Problem discussion.

• Plan B. Behavioural, using the truth table or a high-level algorithm describing the chip's functionality.

Problem <u>discussion.</u>

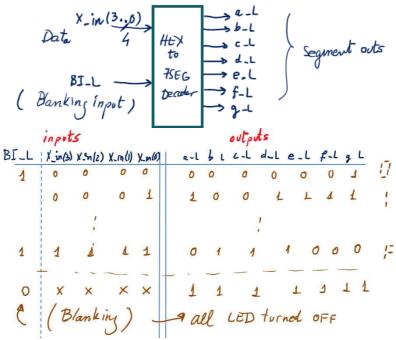

#### 2.4 Designing a 10-line to 4-line priority encoder

The objective is to develop VHDL code and the final circuit for the 10-line to 4line priority encoder circuit (*Enc\_10\_4*) component represented in Fig. 12, which can be interfaced to a standard 10-key numeric keypad. The circuit must have priority decoding of the inputs to ensure that only the highestorder data line is encoded in case several keys are pressed at the same time. This circuit is similar to a standard combinational chip like the <u>74LS148</u>. As usual, we can plan the project in several ways, as represented in our <u>CSD</u> <u>design flow chart</u>:

- Plan A: Structural (flat design with a single VHDL file), using the truth table logic equations in a canonical or simplified version.

- Plan B: Behavioural (flat design with a single VHDL file), using the highlevel description of the specifications.

- Plan C2: Structural (hierarchical design with multiple VHDL files), building the project using an architecture consisting of smaller components of the same kind, such as *Enc* 4 2 or *Enc* 8 3.

Fig. 12

a) A typical 10-key numerical keypad (push-buttons).

b) Interface circuit that gives the binary code of the pressed key. This is an MSI -(medium scale of integration) circuit that can be fitted in a simple programmable logic device (sPLD) like the <u>GAL22V10</u> or any other CPLD or FPGA.

The picture shows the outputs when the circuit is enabled and the keys K7 and K1 are pressed simultaneously.

As usual in these problems, you will solve some drilling exercises on Boole's algebra before you attempt the design of the *Enc\_10\_4*.

#### Section 1: Specifications and theory

- 1) Find on the internet a commercial standard circuit in classic technologies which has a similar truth table. You can start by visiting our <u>list</u>.

- 2) Fill in the truth table using the names and the variable order depicted below using "don't care" ("-" or "x") terms. Gs has to be high ('1') when any key is pressed. The enabled output (Eo) is high when the circuit is enabled (Ei = '1') and the keys are not pressed. How many combinations does the truth table include?

| Ei | K9 | K8 | K7 | K6 | K5 | K4 | K3 | K2 | K1 | K0 | D3 D2 | D1 | D0 | Gs | Eo | Comments |

|----|----|----|----|----|----|----|----|----|----|----|-------|----|----|----|----|----------|

|    |    |    |    |    |    |    |    |    |    |    |       |    |    |    |    |          |

- 3) Draw the sketch of a timing diagram for the circuit and describe the outputs that are expected when different inputs are applied.

- 4) How long does it take to run a complete full verification of the circuit if each input vector has a duration of  $Min_Pulse = 10 \ \mu s$ ?

- 5) How do you generate a '0' or a '1' using push-buttons or switches? How do you drive a LED for example to connect at the output Gs? Study this circuit in Proteus to get ideas and design formulas.

- 6) How many minterms will D3 have? How many maxterms will D2 have?

- 7) Inspect the truth table or use Minilog to represent the six output functions either as the sum of products (SoP) or the product of sums (PoS).

- 8) Draw the logic circuit of the output **D1** using only NOR gates.

$$(x \cdot y)' = x' + y'$$

,  $(x \cdot y \cdot z)'' = (x' + y' + z')'$

- 9) If the propagation delay of a single gate of the technology used is 7.5 ns, what is the maximum frequency of operation of the circuit in 8)?

- **10)** Prepare other similar questions such as: invent **D0** using only NAND, write the text file in *tbl* format for the Minilog minimiser, etc.

#### Section 2: Select a plan and complete the project

The following questions are related to synthesising the project *Enc\_10\_4* into a programmable device and testing it using EDA tools. The plan to organise the architecture is either *11*, *12*) or *13*). Each plan leads to a different project.

- **11)** Architecture #1 (Plan A, structural-flat): write down the structural VHDL code that is derived from the equations deduced in *7*).

- **12)** Architecture #2 (Plan B, behavioural): search the internet or find in books a high-level or algorithmic VHDL code for the component in Fig. 12b. As usual, use flow charts or schematics to translate the truth table into VHDL.

- 13) Architecture #3 (Plan C2, structural-hierarchical): figure out how to design an *Enc\_10\_4* using components like *Enc\_4\_2* and other circuits if necessary. How many VHDL files will the project contain? In this section, the **Ei** and **Eo** signals must be used to facilitate block expansion.

#### Section 3: Develop your plan

14) Create a project for a CPLD or FPGA target chip, using EDA tools (Lattice ispLEVER Classic or Diamond, Intel Quartus Prime or Xilinx ISE or Vivado). Print the RTL schematic and technology schematics and discuss them.

#### Section 4: Test your circuit

- **15)** Translate the timing diagram sketch represented in *3)* into a VHDL test bench file to simulate functionally the circuit using ActiveHDL, ModelSim or ISim. Print the logic analyser timing diagram and discuss it.

- **16)** Perform a gate-level simulation to measure the worst-case propagation delay and calculate the encoder's maximum frequency of operation for a given PLD target chip.

Looking forward: this project introduces standard combinational encoder devices. They can be compared to matrix implementations such in Problem 6.4.

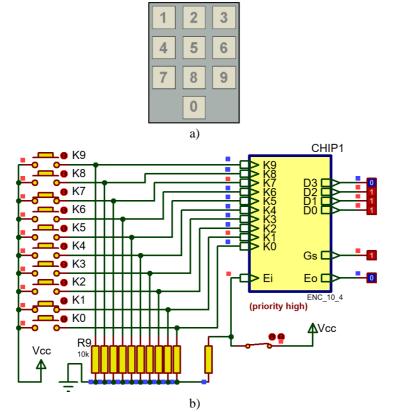

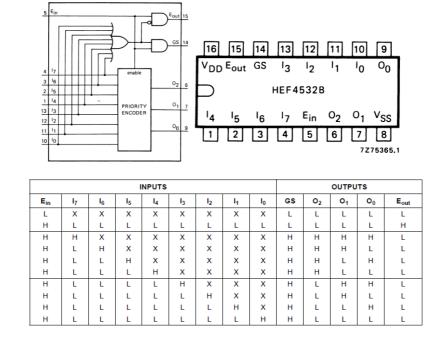

#### 2.5 Designing an 8-line to 3-line priority encoder

Fig. 13 shows the internal circuit of the classic chip <u>HEF4532B</u> and its truth table as specified by Philips.

Fig. 13 The HEF4532B manufactured by Philips. When Ein is low the chip is disabled. Group select (GS) is assessed when there is any input active. Enable output Eout is active only when the chip is enabled and there is not a single input active. The outputs O(2..0) generate the binary code of the input being active. The highest input prevails when more than one input is active at the same time.

- 1) Redraw the truth table using '0' and '1' and explain what the circuit's function is, using a pair of examples. How many binary combinations does this table have?

- Write E<sub>out</sub> = f( E<sub>in</sub>, I<sub>7</sub>, ..., I<sub>0</sub>) using minterms. In addition, draw the equivalent circuit using gates.

- 3) Write GS as a product of sums (PoS). How many minterms does this function have? Draw the circuit using gates.

Write  $O_2$  as a sum of products (SoP). How many maxterms does this function have? Write  $O_1$  and  $O_0$  as a product of sums (PoS).

- 4) Describe the circuit in VHDL in a behavioural or structural fashion.

- 5) Draw a sketch of a timing diagram and translate it into a test bench so that the circuit can be verified using an EDA tool.

Optional questions related to further understanding the problem and designing the project *encoder\_8\_to\_3.vhd* into a programmable device:

6) Write the *.tbl* format file so that it can be used to obtain the PoS or the SoP in Minilog software. Find and write down the link to a similar circuit in

<u>HADES</u> that can be executed using the Java applet. Simulate the circuit in Proteus and check if it works as expected.

7) Start a VHDL-based synthesis project and a testbench-based simulation using EDA tools for target CPLD or FPGA programmable chips.

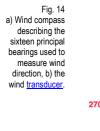

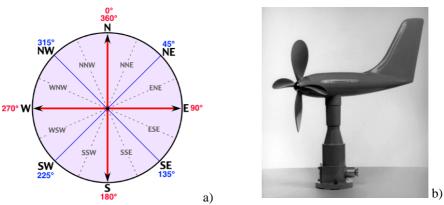

#### 2.6 A digital wind direction meter

We want to design a digital wind direction meter (*wind\_compass*) as shown in Fig. 14, based on a 16-position optoelectronic rotary encoder. As shown in Fig. 15, the sensor disk is coded in Gray, which was originally used instead of binary code to prevent spurious outputs from electromechanical switches. The objective is to develop the VHDL code and the final circuit to be synthesised into a complex programmable device (CPLD) or a field programmable gate array (FPGA) chip.

To promote class and cooperative group discussions, we can plan the project in several ways, as represented in our <u>CSD design flow chart</u>. Each plan means a different project and circuit realisation that is useful for comparing solutions:

- Plan A: Structural (flat design with a single VHDL file), using logic equations in a canonical or simplified version.

- Plan B: Behavioural (flat design with a single VHDL file), using high-level description of the specifications.

- Plan C2: Structural (hierarchical design with multiple VHDL files), building the project using an architecture consisting of components and signals.

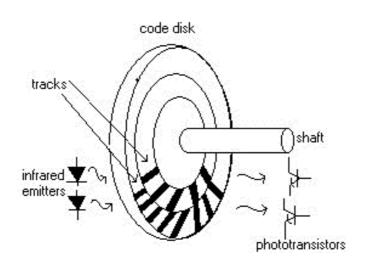

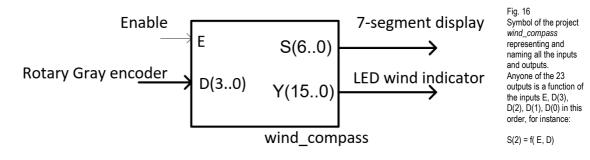

Fig. 16 shows the symbol of the wind\_compass chip to be implemented.

#### Section 1: Specifications and theory

Let us solve some initial drilling questions to learn a bit of theory and clarify ideas, and implement the projects based on plans A and B.

- 1) Write the truth table of the *wind\_compass*. The inputs have to be ordered in this way: E, D(3..0).

- 2) Write the functions Y(7) and Y(14) canonically as a product of maxterms.

Fig. 15

The basics of the Gray

to binary rotary encoder sensor.

- 3) Write the functions S(6) and S(1) canonically as a sum of minterms.

- 4) Let us minimise the *wind\_compass* using Minilog and obtain the equation output formats for SoP and PoS.

- 5) Write the functions S(2) and Y(13) as an SoP and draw the equivalent logic circuit.

- 6) Write the functions S(0) and Y(11) as a PoS and draw the equivalent logic circuit.

- 7) Write the functions S(4) and Y(5) using only NOR.

- 8) Write the functions S(3) and Y(10) using only NAND.

- 9) Draw a schematic to translate according to plan B, the wind\_compass truth table to VHDL, representing the required signals to interface the truth table artefact.

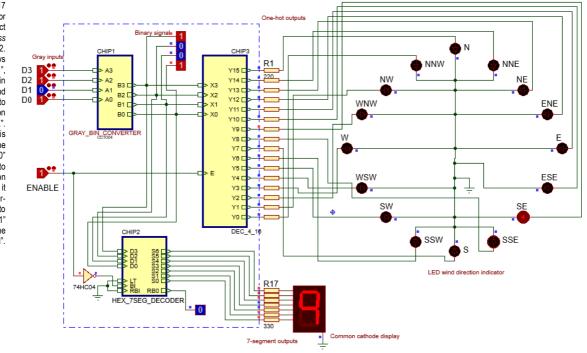

Fig. 17 shows an example of an internal electronic schematic for the *wind\_compass* when plan C2 is used. It is available <u>here</u> and for experimentation. The output of Chip1 (*gray\_bin\_converter*) is connected to both Chip2, a 1-digit 7-segment decoder (*hex\_7seg\_decoder*), and Chip 3, a 16-bit decoder (*dec\_4\_16*) with one-hot output to light a wheel of 16 LED to display the wind direction.

Fig. 17 Internal design for the project wind\_compass based on plan C2. The picture shows Gray code "1101", which is "1001" in binary and corresponds to the wind direction South-East "SE" In the way it is connected, the code "0000" corresponds to the direction "NNW", and it advances counterclockwise up to the code "1111" which is the direction "N".

- **10)** Run the Proteus circuit of the circuit in Fig. 17. Print the screen results when you input the Gray code "0101" and explain how it works.

- 11) Draw an example timing diagram showing the input stimulus and output responses. Assuming that *Min\_Pulse* = 1.26 us, how long does it take to simulate all the circuit specifications?

#### Section 2: Select a plan

12) Plan A: write the VHDL code for the wind\_compass to obtain the wind\_compass.vhd circuit file.L:\CSD\P2\wind\_compassA\wind\_compass.vhd

**13)** Plan B: write the VHDL code for the *wind\_compass* to obtain the *wind\_compass.vhd* circuit file.

L:\CSD\P2\wind\_compassB\wind\_compass.vhd

#### Section 3: Develop your plan

14) Synthesise the projects for the given target CPLD/FPGA chip using an EDA from Lattice, Xilinx or Intel. Discuss using handwritten comments the RTL and the technology schematics for plans A and B.

#### Section 4: Test your circuit

**15)** Test both projects functionally using the same VHDL test bench, for instance, derived from the timing diagram in Question 11). Print the logic analyser timing diagrams and explain them using handwritten comments.

There is a former <u>exam</u> (1718Q1, Prob. 1) that includes a solution with comments and simulation files for a similar project.

Optional extra questions to prepare P3 and P4 projects on VHDL hierarchical design and timed gate-level simulations:

**16)** Plan C2: design the project *wind\_compass* using a multiple-file hierarchical approach.

L:\CSD\P3\wind\_compass\(files)

17) Perform a gate-level simulation to measure the worst case propagation delay and calculate the encoder's maximum frequency of operation for a given PLD target chip.

Fig. 18 shows additional details to help you to analyse the project, like the truth table associated with a combinational circuit such as *Chip1* in Fig. 17, a 4-bit *gray\_bin\_converter*.

| Fig. 18<br>a) Truth table of a<br>4-bit Gray to           | A3 | A2 | 1 |

|-----------------------------------------------------------|----|----|---|

| binary converter                                          | 0  | 0  | ( |

| circuit.                                                  | 0  | 0  | ( |

| <li>b) The <u>translation</u><br/>of the truth table</li> | 0  | 0  |   |

| into Minilog text<br>format.                              | 0  | 0  |   |

| Note how the 16                                           | 0  | 1  |   |

| input                                                     | 0  | 1  |   |

| combinations do<br>not have to be                         | 0  | 1  | ( |

| written necessarily<br>in binary                          | 0  | 1  | ( |

| sequential.                                               | 1  | 1  | ( |

|                                                           | 1  | 1  | ( |

|                                                           | 1  | 1  |   |

|                                                           | 1  | 1  |   |

|                                                           |    | ~  | - |

| A3 | A2 | A1 | A0 |   | B3 | B2 | Β1 | В0 |

|----|----|----|----|---|----|----|----|----|

| 0  | 0  | 0  | 0  |   | 0  | 0  | 0  | 0  |

| 0  | 0  | 0  | 1  |   | 0  | 0  | 0  | 1  |

| 0  | 0  | 1  | 1  |   | 0  | 0  | 1  | 0  |

| 0  | 0  | 1  | 0  |   | 0  | 0  | 1  | 1  |

| 0  | 1  | 1  | 0  |   | 0  | 1  | 0  | 0  |

| 0  | 1  | 1  | 1  |   | 0  | 1  | 0  | 1  |

| 0  | 1  | 0  | 1  |   | 0  | 1  | 1  | 0  |

| 0  | 1  | 0  | 0  |   | 0  | 1  | 1  | 1  |

| 1  | 1  | 0  | 0  |   | 1  | 0  | 0  | 0  |

| 1  | 1  | 0  | 1  | L | 1  | 0  | 0  | 1  |

| 1  | 1  | 1  | 1  | L | 1  | 0  | 1  | 0  |

| 1  | 1  | 1  | 0  |   | 1  | 0  | 1  | 1  |

| 1  | 0  | 1  | 0  |   | 1  | 1  | 0  | 0  |

| 1  | 0  | 1  | 1  |   | 1  | 1  | 0  | 1  |

| 1  | 0  | 0  | 1  |   | 1  | 1  | 1  | 0  |

| 1  | 0  | 0  | 0  |   | 1  | 1  | 1  | 1  |

|    | a) |    |    | - |    |    |    |    |

| ta | able             | e G:             | ray_             | _Bin_            | Con              | ver              | ter              |                  |  |  |  |  |

|----|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|--|--|--|--|

|    |                  |                  |                  | 2 A1<br>32 B1    |                  |                  |                  |                  |  |  |  |  |

| "  |                  | PUT              |                  |                  | JTPUTS           |                  |                  |                  |  |  |  |  |

| "  |                  | A2               |                  | A0               | в3               | в2               |                  |                  |  |  |  |  |

|    | 0<br>0<br>0<br>0 | 0<br>0<br>0<br>0 | 0<br>0<br>1<br>1 | 0<br>1           | 0<br>0<br>0<br>0 | 0<br>0<br>0<br>0 | 0<br>0           | 0<br>1           |  |  |  |  |

|    | 0<br>0<br>0<br>0 | 1<br>1<br>1<br>1 | 1<br>1<br>0<br>0 | 0<br>1<br>1<br>0 | 0<br>0<br>0<br>0 | 1<br>1<br>1<br>1 | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 |  |  |  |  |

|    | 1<br>1<br>1<br>1 | 1<br>1<br>1<br>1 | 0<br>0<br>1<br>1 | 0<br>1<br>1<br>0 | 1<br>1<br>1<br>1 | 0<br>0<br>0      | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 |  |  |  |  |

|    | 1<br>1<br>1<br>1 | 0<br>0<br>0      | 1<br>1<br>0<br>0 | 0<br>1<br>1<br>0 | 1<br>1<br>1<br>1 | 1<br>1<br>1<br>1 | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 |  |  |  |  |

| eı | nd               |                  |                  |                  |                  |                  |                  |                  |  |  |  |  |

b)

# P3 Arithmetic circuits: adders, multipliers, comparators, etc. and VHDL hierarchical design (plan C2)

### Objectives

After studying the content of these projects, you will be able to: corrected

- Explain how to perform basic operations like add, compare or multiply using the radix-2 binary number system.

- Convert natural (whole) numbers between several number systems such as binary (radix-2), decimal (radix-10) or hexadecimal (radix-16).

- Find and analyse the characteristics of classic industry standard arithmetic chips like 74HCT283, 74LS85, 74LS181, etc.

- Write an alphanumeric message using ASCII code.

- Encode data, information or symbols in Gray, one-hot, BCD, etc.

- Explain the basics and operability of adders and comparators.

- Infer the idea of an arithmetic and logic unit (ALU) circuit.

- Infer how to design hardware multipliers.

- Infer an *n*-bit ripple-carry adder.

- Infer a 4-bit carry-lookahead adder and be able to compare its characteristics with respect to the ripple-carry adder.

- Use the method of decoders (MoD) to implement logic functions.

- Use the hierarchical method of multiplexers (MoM) to implement logic functions.

- Apply hierarchical structural design (plan C2) to implement arithmetic circuits using VHDL.

The following function is expressed in SoP: Here

f(w, x, y, z) = x'y'z + x'y'z' + wxy' + wyz' + xy

- a) Draw the entity's symbol and draw the circuit diagram using logic gates. Write the equation in VHDL.

- b) Apply Boole Algebra analysis or use a computer tool like <u>WolframAlpha</u> or <u>Logic Friday</u> to deduce the truth table and the canonical equations sum of minterms and product of maxterms.

- c) Solve the circuit by the method of decoders.

- d) Invent a timing diagram to demonstrate how the circuit works, and translate it into a VHDL test bench to perform an ActiveHDL / ModelSim / ISim functional simulation.

#### 3.2 Logic functions using the method of multiplexers

The following function is expressed in SoP:

f(w, x, y, z) = x'y'z + x'y'z' + wxy' + wyz' + xy

- a) Draw the entity's symbol and draw the circuit diagram using logic gates. Write the equation in VHDL.

- b) Apply Boole Algebra analysis or use a computer tool like <u>WolframAlpha</u> or <u>Logic Friday</u> to deduce the truth table and the canonical equations sum of minterms and product of maxterms.

- c) Solve the circuit by the method of multiplexers using a MUX4. How many VHDL files are required to implement the project of this circuit?

- d) Invent a timing diagram to demonstrate how the circuit works, and *translate* it into a VHDL test bench to perform an ActiveHDL / ModelSim / ISim functional simulation.

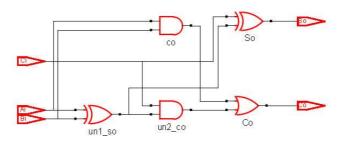

### 3.3 Design a 1-bit full adder (flat)

Study and run the tutorial on the design of the Adder\_1bit following two different single-VHDL file (flat) plans:

- A) Structural

- B) Behavioural

+ Problem <u>discussion</u>

Solve the additional questions:

- a) Implement  $C_o$  using only NOR gates.

- b) Implement  $S_o$  using maxterms.

- c) If a logic gate has a propagation delay of 6.5 ns, deduce the maximum frequency of operation of your circuit.

Fig. 19 The entity of an Adder\_1bit.

#### 3.4 Design a 1-bit full adder (structural)

Study and run the tutorial on the design of the Adder\_1bit following two different structural multiple-VHDL file (hierarchical) plans:

- A) Method of decoders

- B) Method of multiplexers

- + Problem <u>discussion</u> using the method of decoders

+ Problem <u>discussion</u> using the method of multiplexers

#### 3.5 Design a 1-bit comparator

Study and run the tutorial on the design of the Comp\_1bit based on SoP equations.

Problem discussion

### 3.6 Designing a MUX\_8 using a multiple-file structure

+ Problem <u>discussion</u>

The objective is to design the functionality of a MUX\_8 type 74HCT151 using VHDL synthesis and simulation EDA tools and a hierarchical strategy using multiple VHDL files.

• Plan C2. Invent a hierarchical schematic for the MUX\_8 using smaller components of the same kind, for instance, MUX\_4 or and MUX\_2.

Fig. 20 MUX\_8 chip symbol derived from the standard 74HCT151.

### 3.7 4-bit ripple adder

Follow and run the tutorial on the Adder\_4bit based on a ripple carry plan.

#### 3.8 8-bit binary adder using 4-bit carry-look ahead adders

Project:

a) Write the VHDL code of the complete 4-bit carry lookahead adder (*Adder\_1bit.vhd*, *Adder\_4bit.vhd*, *Carry\_generator.vhd*).

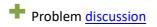

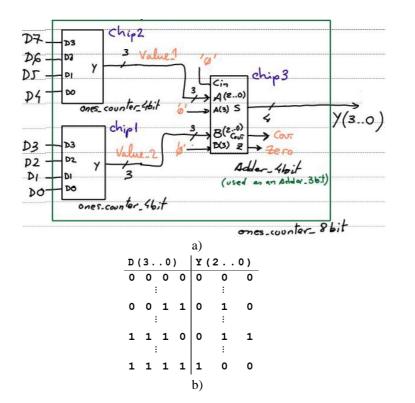

Fig. 21 The idea of a 4-bit carrylookahead adder (chip <u>74HCT283</u>), as explained in: Introduction to digital systems, Ercegovac, M., Lang, T., Moreno, J. H., John Wiley & Sons, 1999, <u>web</u>.

Development of the 4-bit carry-lookahead adder.

b) Start a project using an EDA tool and synthesise the circuit in a given target chip CPLD or FPGA. Print the RTL view and comment it.

Test the 4-bit carry-lookahead adder.

c) Start a VHDL simulator EDA tool and run a test bench to verify the unit under test applying some 4-bit operands. Print the timing diagram and add notes and explanations.

#### 3.9 Designing a 6-bit comparator using VHDL

**>** A > B

EQ  $\square$  A = B

LT CA<B

The idea is to develop and implement an expandable *Comp* 6bit component. Fig. 22 shows the entity's symbol and the proposed internal architecture for the <u>Plan C2</u> consisting of a structural hierarchical planning.

A[5..3]

B[5..3]

B[2..0]

CHIP2

GT

LT

COMP 3BIT

Comp 6bit

GT

EQ

LT

A[2..0]

A[2..0] EQ

G

Ei

CHIP1

GT

LТ

COM

A[2..0] FO W3

W2

W1

b)

Fig. 22 a) Entity for the 6-bit expandable comparator. b) Example of an internal architecture for the Comp\_6bit based on a structure of smaller elements of the same kind (Plan C2).

Comp\_3bit which is used as a buildina component in the Oomp\_6bit.

A[2..01 Ei COMP 6BIT Inputs for expansion A greater than B A equal to B A less than B a) Fig. 23 Truth table for the cascadable 3-bit comparator

A[5..0]

B[5..0]

Gi

GT 🗖

|             |    |    |    |    |    |    | ,                   |

|-------------|----|----|----|----|----|----|---------------------|

| A[20] B[20] | Gi | Ei | Li | GT | EQ | LT |                     |

| A > B       | х  | х  | х  | 1  | 0  | 0  | A is greater than B |

| A < B       | х  | х  | х  | 0  | 0  | 1  | A is lesser than B  |

|             | 1  | 0  | 0  | 1  | 0  | 0  | Gi input decides    |

| A = B       | 0  | 1  | 0  | 0  | 1  | 0  | Ei input decides    |

|             | 0  | 0  | 1  | 0  | 0  | 1  | Li input decides    |

Plan C2: Implementation of a structural design in a CPLD or a FPGA.

- a) Explain the design flow you will follow to produce your circuit using Lattice ispLEVER Classic / Altera Quartus II / Xilinx ISE.

- b) Draw a structured hierarchical design as in Fig. 22b using several components. For instance, Fig. 23 shows the truth table for a 3-bit cascadable comparator.

- c) Implement the elemental *Comp* 1bit using the logic equations derived from *Minilog.exe* (single output mode, sum of products, table output format). Verify your equations using WolframAlpha. This section is solved as a tutorial in the web (*Comp 1bit*).

- d) Create a multiple-file VHDL-based project using EDA tools for a CPLD target chip, for example Lattice ispMACH4128V TQFP100, or the Intel-Altera MAX EPM7128SLC84-7, or the Xilinx CoolRunner II XC2C256-TQ144 - 7. Print and comment the RTL and technology views of the synthesised circuit, so that it can be compared to the initial block diagram proposed in Fig. 22b.

- e) Test and simulate your design using the ActiveHDL / ModelSim / ISim simulators by means of a VHDL test bench.

(Optional)

- f) Assign pins and generate the output configurations files if the circuit has to be prototyped in a development board (Lattice HWD-LC4128V, Altera UP2 or Xilinx CoolRunner-II CPLD Starter Board).

- g) Write down a report to document your design using our quality standards and templates.

#### (Optional)

There are other ways to describe the same circuit, which are not in the scope of this introductory CSD course. Sometimes, the single-file behavioural version of the arithmetic circuit is not that difficult to write.

Plan B: Implementation of a behavioural design (flat design, single VHDL file)

- h) Draw the truth table and a timing diagram sketch for the *Comp\_6bit* circuit.

- i) Write down the high level or behavioural VHDL code directly as a single block as in Fig. 22a planning writing first an algorithm or a flowchart to translate the circuit's truth table.