## **EX 3** DIGITAL CIRCUITS AND SYSTEMS

# Designing a serial multiplier

| 1.1 Cooperati                            | ve group                   |                                     |                                                            |             |

|------------------------------------------|----------------------------|-------------------------------------|------------------------------------------------------------|-------------|

| TEAM NUMBER:<br>DUE DATE:<br>STUDY TIME: |                            |                                     |                                                            |             |

| Study time<br>(in hours)                 | Group work                 | Classroom and laboratory sessions   | Sessions out of classroom                                  |             |

|                                          | Individual                 | Student 1<br>Student 2<br>Student 3 | •                                                          |             |

|                                          | ame anyone out<br>ocument. | side this group who assisted        | s, analyses, simulations) of this learning team or any inc |             |

| Active members (1) Angél                 | ica Rodríguez              | Roles: (reporter, simulator, e      |                                                            | ator, etc.) |

| (2)                                      |                            |                                     |                                                            |             |

| Acknowledgement (1)(2)                   |                            |                                     | completing this document:                                  |             |

| 1.2 Abstract                             |                            |                                     |                                                            |             |

In this exercise we will perform a multiplier in VHDL. We will see each of the parts of this multiplier: a 4x4 serial multiplier, a clock divider, a timer, a binary to BCD converter of 8 bits, a quad mux4 and the BCD to 7 segment converter. We will study these parts step by step.

## CONTENT

| Design | ning a     | a serial multiplier                  | 1  |

|--------|------------|--------------------------------------|----|

| 1.1    | Co         | operative group                      | 1  |

| 1.2    | Ab         | stract                               | 1  |

| 1.3    | Pro        | oblem solution                       | 3  |

| 1.3    | <i>3.1</i> | The structure of the top design      | 3  |

| 1.3    | 3.2        | Multiplier                           | 3  |

| 1.3    | 3.2.1      | The 4x4 unsigned serial multiplier   | 5  |

| 1.3    | 3.2.2      | The clock divider                    |    |

| 1.3    | 3.2.3      | The Timer                            | 21 |

| 1.3    | 3.2.4      | The Binary to BCD converter of 8 bit | 24 |

| 1.3    | 3.2.5      | The Quad_Mux4                        |    |

| 1.3    | 3.2.6      | The BCD to 7 segments                |    |

| 1.3    | 3.3        | Total design                         |    |

## 1.3 Problem solution

#### 1.3.1 The structure of the top design

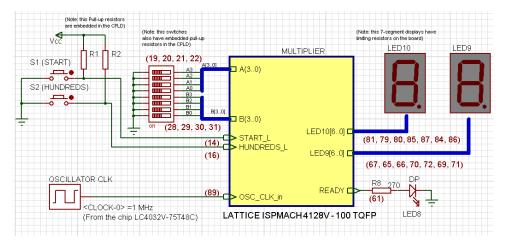

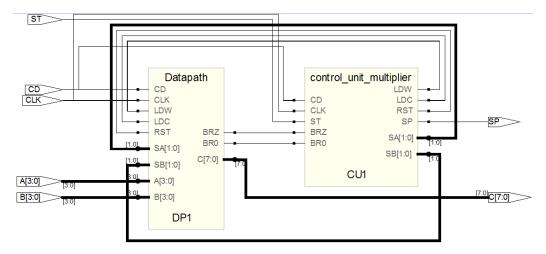

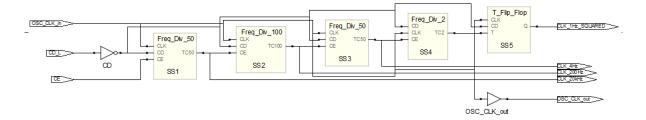

For do the multiplier, we will separate the project in different blocks. These blocks will be grouped in the block that we see in Fig. 1.

Fig. 1 Schematic of multiplier

In this schematic we can see a multiplier where LED10 show the operand A (the tens) and LED9 show the operand B (the units). Push button HUNDREDS shows the hundreds and start pulse triggers the operation. The result is displayed while READY is high (5 seconds), then the operand are shown again.

#### 1.3.2 Multiplier

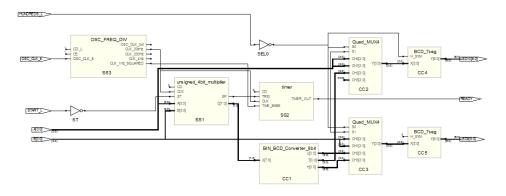

The main blocks that we will see for do the multiplier are one frequency divider, one unsigned 4 bits multiplier, one timer, one binary to BCD converter of 8 bits, two quad mux4 and two BCD to 7 segments converter. The design that we will do is in this Fig. 2.

Fig. 2 Design of multiplier

For all this blocks we have a code in VHDL of the entire project in Fig. 3. This code group all the blocks that after break down one to one.

```

STD_LOGIC_VECTOR(3 DOWNTO 0); --INPUTS

STD_LOGIC;

STD_LOGIC;

STD_LOGIC;

STD_LOGIC_VECTOR(6 DOWNTO 0); --OUTPUT

STD_LOGIC

END multiplier;

END multiplier:

ARCHITECTURE STRUCTURAL OF multiplier IS COMPONENT OSC_FREQ_DIV IS

FORT ( CE OSC_CLK_in CD_T according to the control of th

:IN std_logic;

:IN std_logic;

:IN std_logic;

:OUT std_logic;

:OUT std_logic;

:OUT std_logic;

:OUT std_logic;

:OUT std_logic;

END COMPONENT;

COMPONENT unsigned_4bit_multiplier IS PORT (

A,B

ST, CD, CLK

C

SP

END COMPONENT;

COMPONENT timer IS

PORT (

: IN STD_LOGIC;

: OUT STD_LOGIC

TRIG, TIME_BASE, CD, CLK

TIMER_OUT

);

END COMPONENT;

COMPONENT Bin_BCD_Converter_8bit IS

PORT (

Y : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

U, T, H : OUT STD_LOGIC_VECTOR(3 DOWNTO 0)

COMPONENT Quad_MUX4 IS PORT (

CH0 : IN CH1 : IN CH2 : IN CH2 : IN CH3 : IN Y : OUT

END component;

COMPONENT BCD_7seg IS PORT (

: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

: IN STD_LOGIC;

: OUT STD_LOGIC_VECTOR(6 DOWNTO 0)

signal Trigger, ST, CLK_4Hz, CLK_200Hz, OSC_CLK_out, CLK_20kHz, CLK_1Hz_SQUARED, SELO, SEL1 signal C signal U, T, H, Digit2, Digit1

STD_LOGIC;

STD_LOGIC_VECTOR(7 downto 0);

STD_LOGIC_VECTOR(3 downto 0);

BEGIN

SS1: unsigned_4bit_multiplier

port map(

ST => ST,

A => A,

B => B,

OC == D,

CLK => CLK_20kHz,

C, SS =< Trigger

);

SS2: timer ),

port map(

TRIG => Trigger,

TIME_BASE => CLK_1Hz_SQUARED,

CLK => CLK_20kHz,

TIMER_OUT => SEL1

);

SS3: OSC_FREQ_DIV

CC1: Bin_BCD_Converter_8bit

port map(

X =>

U =>

T =>

C,

U,

T,

H

CC2: Quad_MUX4

port ma

A,

A,

T,

"0000",

SEL0,

SEL1,

Digit2

CC3: Quad_MUX4

CC4: BCD_7seg , port map( X Y H_SYM );

END STRUCTURAL;

```

Fig. 3 Code in VHDL of multiplier

Now we study all the parts of the multiplier step by step. The first block we let's see is the 4x4 unsigned serial multiplier.

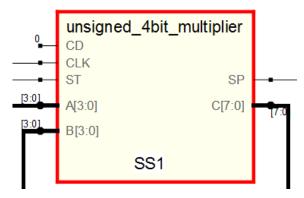

## 1.3.2.1 The 4x4 unsigned serial multiplier

The first block that we study has for inputs the two numbers that we want multiplier and also it has the button ST (start) for do the operations.

Fig. 4 Schematic of 4x4 unsigned serial multiplier

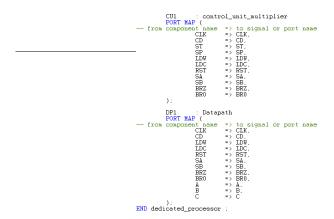

The code of this block is in Fig. 5 and we can see that this block has two others blocks within: the control unit multiplier and the datapath.

Fig. 5 Code un VHDL of 4x4 unsigned serial multiplier

In this Fig. 6 we can see the schematic inside of the unsigned 4 bit multiplier: we have the control unit multiplier and the datapath as we have seen before.

Fig. 6 Schematic inside 4x4 unsigned serial multiplier

Now we study these blocks, first the control unit multiplier and after tha datapath.

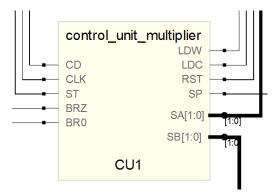

## 1.3.2.1.1 The Control Unit Multiplier

$Fig.\ 7\ Schematic\ of\ control\ unit\ multiplier$

The code of the control unit multiplier is in Fig. 8

```

-- Control Unit for the 4-bit unsigned multiplier

ENTITY control unit multiplier IS

FORT( CD.CLK.ST ERZ. BRO ED. LDW. LDC ERST SA. SB SP

std_logic;

std_logic;

std_logic;

oUT std_logic;

std_logic_vector(1 downto 0);

OUT std_logic

END control_unit_multiplier;

ARCHITECTURE FSM_like OF control_unit_multiplier IS

TYPE State_type IS (Idle, Load Data, Flags, Load Result, Add, Shift);

-> This is important; specifying to the synthesiser the code for the states

ATTRIBUTE syn_enum_encoding; STRIM;

ATTRIBUTE syn_enum_encoding; OF State_type; TYPE IS "sequential";

- (it may be "sequential" (start); "gray"; "one-hot", etc.

SIGNAL present_state, future_state ; State_type;

-- These two lines work OK, but the state machine is not recognised.

-- and regular logic is synthesised (so it's not so good as the syn_encoding)

-- ATTRIBUTE enum_encoding : string;

-- ATTRIBUTE enum_encoding of State_type : TYPE IS "sequential";

-- Constants for special states (the first and the last state)

CONSTANT Reset : State_type := Idle; -- The first state. This is another name for the state Num0

state_register: PROCESS (CD,CLK)

BEGIN

IF CD = '1' THEN --- asynchronous reset of the FSM ELSIF (CLK/EVENT and CLK = '1') THEN --- Synchronous register (D-type flip-flop) END IF;

END PROCESS state_register;

--- CC1: Combinational system for calculating next state

CC_1: PROCESS (present_state, BR0, BRZ, ST)

BEGIN

CASE present_state is

if ST='0' then

future_state <= Idle;

future_state <= Load_Data ; end if;

when Load Data =>

future_state <= Flags ;

when Flags =>

if BRZ='1' then

future_state <= Load_Result;

elsif ( BRZ='0' and BR0='1') then

future_state <= Add;

elsif ( BRZ='0' and BR0='0') then

future_state <= Shift;

end if;

when Load Result =>

future_state <=Idle;

when Add =>

future_state <=Shift;

when Shift

future_state <=Flags;

end case;

END PROCESS CC_1;

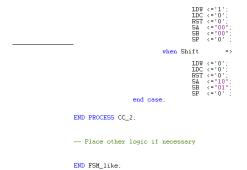

CC_2: PROCESS (present_state)

BEGIN

CASE present_state is when Idle =>

LDW <='0';

LDC <='0';

RST <='0';

SA <="00";

SB <="00";

SP <='0';

when Load_Result =>

```

Fig. 8 Code in VHDL of control unit multiplier

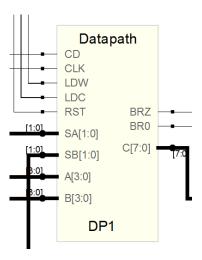

## **1.3.2.1.2** The Datapath

The second block of the 4x4 unsigned serial multiplier is the datapath that we have in Fig. 9.

Fig. 9 Schematic of datapath

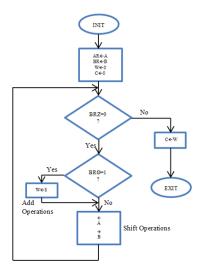

Below, for understand that we do, we have in Fig. 10 the flow diagram (while designing the datapath) for do the corresponding code.

Fig. 10 Diagram of datapath

With this diagram we can do the code in VHDL that we have in Fig. 11.

```

-- 4-bit unsignel multiplier datapath

-- Structural and hiearchical design

LIBRARY ieee;

USE IEEE.STD_LOGIC_1164.all;

ENTITY Datapath IS

PORT( CD,CLK

END Datapath;

ARCHITECTURE Structural OF Datapath IS -- Components

COMPONENT Shift_Data_Reg_4bits IS

PORT( CD,CLK : IN

gic; std_logic_vector(3 downto 0);

std_logic_vector(3 downto 0);

std_logic_vector(1 downto 0);

std_logic

RSI,LSI

COMPONENT Shift_Data_Reg_8bits IS

PORT( CD,CLK : IN

std_logic;

: IN std_logic_vector(7 downto 0);

: OUT std_logic_vector(7 downto 0);

: IN std_logic_vector(1 downto 0);

std_logic_vector(1 downto 0);

X

Y

S

RSI,LSI :

COMPONENT Data_Reg_8bit IS

Port ( CIK

CD :

RST ID :

Y :

IN STD_LOGIC;

IN STD_LOGIC;

IN STD_LOGIC;

IN STD_LOGIC;

IN STD_LOGIC;

IN STD_LOGIC,

OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

IN STD_LOGIC_VECTOR(7 DOWNTO 0)

):

END COMPONENT:

BEGIN

-- Instantiation of components

RegW : Data_Reg_Sbit

-- from component name => tos

CLK => CIK.

);

: Shift_Data_Reg_8bits

PORT MAP (

| Description |

: Shift_Data_Reg_4bits

PORT MAP (

RegB

);

Adder8 : Adder_8bit

PORT MAP (

-- from component name

=> to signal or port name

=> AR.

=> W.

=> S.

=> '0',

=> Co

);

-- Extra logic in the circuit

BRZ <= NOT( BR(0) OR BR(1) OR BR(2) OR BR(3));

BRO <= BR(0);

END Structural;

```

Fig. 11 Code in VHDL of datapath

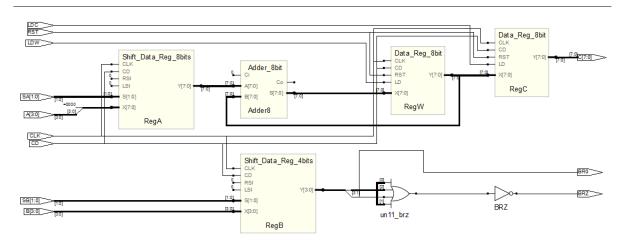

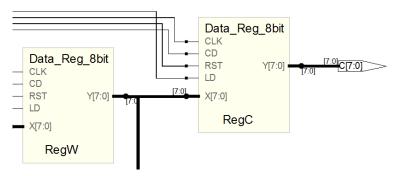

Inside of this block we have the adder, the datareg 8 bit, the shift data register of 4 bit and the shift data register of 8 bit. We can see this in Fig. 12 and below we study this blocks step by step.

Fig. 12 Schematic inside the datapath

## 1.3.2.1.2.1 The Adder

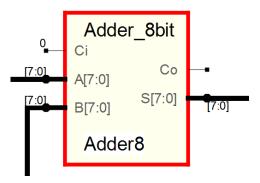

We have study an adder previously and we know that an adder of 8 bits it compouned of four adder of two bits or, in this case, we have eight adders of 1 bit. Firt we see the 8 bit adder that we can see in Fig. 13.

Fig. 13 Schematic of adder

The code of the 8 bit adder is in Fig. 14 and we can see the 8 adder that we need for do this part of the multiplier.

```

LIBRARY ieee;

USE IEEE.STD_LOGIC_1164.all;

IN STD_LOGIC_VECTOR(7 DOWNTO 0);

IN STD_LOGIC;

OUT STD_LOGIC_VECTOR (7 DOWNTO 0);

STD_LOGIC_VECTOR (7 DOWNTO 0);

END COMPONENT;

SIGNAL C1, C2, C3, C4,C5, C6, C7, C8 : STD_LOGIC; -- The wires to connect 1-bit modules together SIGNAL Y : STD_LOGIC_VECTOR (7 DOWNTO 0);

S <= Y;

Co <= C8;

```

Fig. 14 Code in VHDL of adder

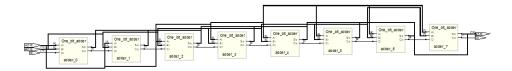

Inside of this adder we have the one bit adders that we speak previously.

## 1.3.2.1.2.1.1 One bit adder

Fig. 15 Schematic of one bit adders

The code that we see in Fig. 16 of the one bit adder is exactly the code that we see in the previous chapter.

Fig. 16 Code in VHDL of one bit adder

## 1.3.2.1.2.2 The DataReg 8 bit

The next block we are study is the data register of 8 bits that we see in Fig. 17.

Fig. 17 Schematic of datareg 8 bit

The code of the datareg 8 bit is in Fig. 18 and we can see that if clear direct is '1' we have a all zeros, if it is '0' we pass to the future state, if RST is '1' we have a reset, and if LD is '1' we load a number X in future state.

```

OGIC_VECTOR(7 DOWNTO 0);

GIC_VECTOR(7 DOWNTO 0)

END Data_Reg_8bit;

ARCHITECTURE FSM_like OF Data_Reg_8bit IS

CONSTANT Reset : STD_LOGIC_VECTOR(7 DOWNTO 0) := "000000000";

SIGNAL present_state,future_state: STD_LOGIC_VECTOR(7 DOWNTO 0);

BECIN ...

State_Register: PROCESS (CD, CLK)

IF CD = '1' THEN

-- Synchronous register (D-type flip-flop)

END PROCESS State Register:

CC1: PROCESS (present_state, X, RST, LD) -- All the block inputs in the sensitivity list

BEGIN

IF RST = '1' THEN

future_state <= Reset;

-- This is the signal with higher priority

ELSIF LD='1' THEN

future_state <= X;

future_state <= present_state;

END IF:

END PROCESS CC1;

Y <= present_state;

END FSM_like;

```

Fig. 18 Code in VHDL of datareg 8 bit

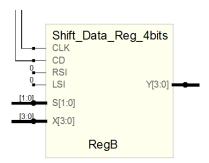

#### 1.3.2.1.2.3 The Shift DataReg 4 bit

The shift datareg that we have in Fig. 19 is very similar to datareg but now the numbers are moved to left or right.

Fig. 19 Schematic of Shift DataReg 4 bit

This is the true table of this block, depending on the value of S1 and S0 in future state we have or present state, or a number loaded, or the number moved to right or left.

| S1          | <b>S</b> 0  | $Y^+$       |

|-------------|-------------|-------------|

| 0<br>0<br>1 | 0<br>1<br>0 | Y<br>→<br>← |

| 1           | 1           | Load data   |

Fig. 20 True table of Shift DataReg 4 bit

In Fig. 21 we have the code of the Shift DataReg 4 bit and here we can see how to do this true table in code VHDL.

Fig. 21 Code in VHDL of Shift DataReg 4 bit

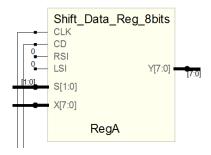

## 1.3.2.1.2.4 The Shift DataReg 8 bit

This block is the same that the Sift DataReg 4 bit, but with 8 bits.

Fig. 22 Schematic of Shift DataReg 8 bit

The code of the Shift DataReg 8 bit is in Fig. 23. Is exactly to the previous code but now we have more bits.

```

LIBRAW iees:

USE IEEE STD LOGIC_1164.al;

USE IEEE STD LOGIC_SIGNED al;

USE IEEE STD LOGIC_VECTOR(1 DOWNTO 0);

USE IEEE STD LOGIC_VECTOR(7 DOWNTO 0);

USE IEEE STD LOGIC_US TO LOGIC TO LOG

```

Fig. 23 Code in VHDL of Shift DataReg 8 bit

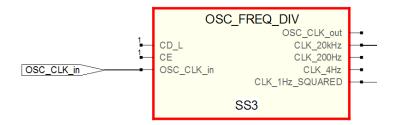

## 1.3.2.2 The clock divider

The next block is the clock divider that we can see in Fig. 24.

Fig. 24 Schematic of clock divider

We have alredy study this block in another excescise and we know that this block have 5 blocks inside. In Fig. 25 we can see the code of the clock divider where we can see the others blocks.

```

ENTITY OSC_FREQ_DIV IS

PORT( CD_L,CE

_200m2

_4Hz

_1Hz_SQUARED

END OSC_FREQ_DIV;

ARCHITECTURE schematic OF OSC_FREQ_DIV IS -- Components

COMPONENT Freq_Div_50 IS

PORT( CD,CLK,CE

TC50

IN std_logic;

OUT std_logic

END COMPONENT;

COMPONENT Freq_Dir

IN std_logic;

OUT std_logic

COMPONENT Freq_Div_2 IS

PORT( CD,CLK

IN std_logic; OUT std_logic

END COMPONENT:

STD_LOGIC

END COMPONENT;

nals for connecting compone

SIGNAL CD, OSC_CLK

SIGNAL CE2, CE3, CE4, CE5

BEGIN

Instantiation of components

SS1 : Freq_Div_50

PORT MAP (

component name => to

CE

TC50

=> CE2

: Freq_Div_100

PORT MAP (

552

=> to signal or

CLK

CD

CE

TC100 => CE3

SS4

SS5 : T_Flip_Flop

PORT MAP (

=> to signal or po:

=> OSC_CLK,

=> CD,

=> CE5,

=> CLK_1Hz_SQUARED

connections and logic between components

Displays OFF when high. In this fashion, only the SQUARED LED will be ON/OFF DISPLAYS <= "11111111111111111";

END schematic

```

Fig. 25 Code in VHDL of the clock divider

Inside the clock divider we have two frequency dividers by 50, a frequency divider by 100, a frequency divider by 2 and one T\_Flip\_Flop that we study now step by step that we can see in Fig. 26.

Fig. 26 Schematic inside the clock divider

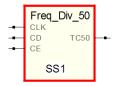

#### 1.3.2.2.1 The frequency divider by 50

In this part we perform a frequency divider by 50.

Fig. 27 Schematic of frequency divider by 50

At first we will see the ideal case, as in Active-HDL we didn't observe any delay. In Fig. 28 we have the code in VHDL of the ideal case.

```

STD_LOGIC:

-- Q

TC50

: OUT STD_LOGIC

END Freq_Div_50;

-- Internal desciption in FSM style

ARCHITECTURE FSM_like OF Freq_Div_50 IS

-- This is the real and necessary Max_Count:

-- CONSTANT Max_Count : STD_LOGIC_VECTOR(23 DOWNTO 0) := "1100000000010111101011"; -- terminal_count after 10 states 12587500

This the the Max_Count modified to speed simulations:

So you must comment this line and activate the above one if you plan to use the real UP2 board SSTANT Max_Count : STD_LOGIC_VECTOR(S_DOWNTO_0) := "110001";

: STD_LOGIC_VECTOR(5 DOUNTO 0) := "000000"; -- 1100 0000 0001 0001 1110 1100 --1100 0000 0001 0001 1110 1011

-- Internal wires

SIGNAL present state future state: STD LOGIC VECTOR(5 downto 0) := Reset:

_____ the only clocked block : the state register state_register: PROCESS (CD, CIK) BEGIN

BEGIN

-- reset counter

ELSIF (CLK:FUENT and CLK = '1') THEN -- Synchronous register (D-type flip-flop)

END IF;

END PROCESS state_register;

future_state <= Reset;

ELSE

future_state <= present_state; -- count disable END IF;

END PROCESS CS_1;

CS_2: combinational system for calculating extra outputs

and outputing the present state (the actual count)

TC50 <= '1' WHEN ((present_state = Max_Count)AND CE = '1') ELSE '0'; --terminal count -- Q <= present_state; In this application, there is no need to output the count value Q

END FSM_like:

```

Fig. 28 Code in VHDL of frequency divider by 50

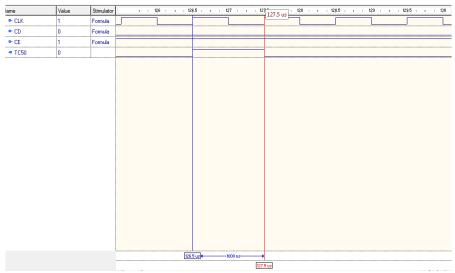

As we shall see in Fig. 29, we speak of an ideal system. If we do a zoom we can see no delay from CLK to TC10.

Fig. 29 Simulation ideal frequency divider by 50

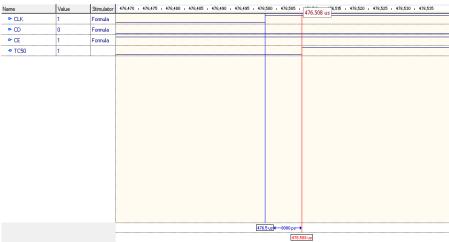

And now, in Fig. 30, we let's see the case in which we observe this delay. For this we need create the .vho and the .sdf files. Once created these files we see the next simulation.

Fig. 30 Simulation real frequency divider by 50

Now we can see clearly that a delay exist from the clock give a pulse until the output reply to this pulse. In this case we have a delay of 8000 ps.

## 1.3.2.2.2 The frequency divider by 100

Now we will perform a frequency divider by 100 that we see in Fig. 31.

Fig. 31 Schematic of frequency divider by 100

We'll see the same that the previous case but with TC100 pulses every 100 clock's. In we see the VHDL code of the divisor.

```

STD_LOGIC;

-- Q

TC100

: OUT STD LOGIC

END Freq_Div_100;

-- Internal desciption in FSM style

ARCHITECTURE FSM_like OF Freq_Div_100 IS

— This is the real and necessary Max_Count;

— COMSTANT Max_Count : STD_LOGIC_VECTOR(23 DOWNTO 0) := "11000000000100011101011"; -- terminal_count after 10 states 12587500

— This the the Max_Count modified to speed simulations.

So you must comment this line and activate the above one if you plan to use the real UP2 board CONSTANT Max_Count : STD_LOGIC_VECTOR(6 DOWNTO 0) := "1100100";

: STD_LOGIC_VECTOR(6 DOWNTO 0) := "00000000"; -- 1100 0000 0001 0101 1110 1100 --1100 0000 0001 0001 1110 1011

SIGNAL present_state, future_state: STD_LOGIC_VECTOR(6 downto 0) := Reset;

state_register: PROCESS (CD, CIK)

BEGIN

-- reset counter

FLSIF (CLK'EYENT and CLK = '1') THEN present_state <= future_state;

END IF;

-- reset counter

-- Synchronous register (D-type flip-flop)

END PROCESS state_register

future_state <= Reset;</pre>

future_state <= present_state; -- count disable END IF;

END PROCESS CS 1:

------ CS_2: combinational system for calculating extra outputs

TC100 <= '1' WHEN ((present_state = Max_Count)AND CE = '1') ELSE '0'; --terminal count -- Q <= present_state; In this application, there is no need to output the count value Q

```

Fig. 32 Code in VHDL of frequency divider by 100

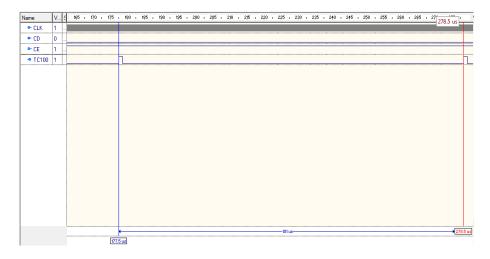

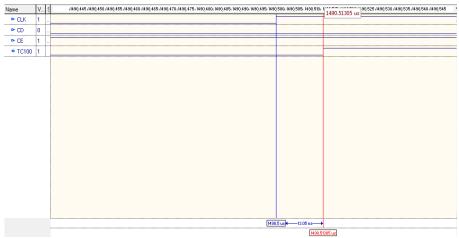

In the simulation we have again two cases, first is the ideal case where we don't have delay and the second is the real case. In *Fig. 33* we have the ideal simulation of the divider.

Fig. 33 Simulation ideal frequency divider by 100

Here we can see how often we have a pulse in TC100, it repeats every 100 clock's when CE is '1' and we are not resetting.

Now we see the real case and we will have the delay between the input and output.

Fig. 34 Simulation real frequency divider by 100

In this Fig. 34 we can appreciate a delay between CLK and TC100 of 13,05 ns.

## 1.3.2.2.3 The frequency divider by 2

$Fig.\ 35\ Schematic\ of\ frequency\ divider\ by\ 2$

The code of this block is very similar with the frequency divider by 50 and 100.

```

IN std_logic;

END Freq_Div_2;

ARCHITECTURE FSM_like OF Freq_Div_2 IS

CONSTANT Max_Count

CONSTANT Reset

: STD_LOGIC := '1';

: STD_LOGIC := '0';

-- Internal state machine wires -

SIGNAI present_state_future_state: STD_LOGIC := Reset;

-- Remember that this idea of ":= Reset;" initalising the wires, has sense only for the simulator, not

-- for a real synthesised flatened circuit, in which CD is used to reset the flip-flops

IF CD = '1' THEN -- reset counter

Present_state <* Reset;

ELSIF (CLK'EVENT and CLK = '1') THEN -- Synchronous register (D-type flip-flop)

END IF;

END IF;

END PROCESS state_register;

CC1: PROCESS (present_state, CE)

BEGIN

IF CE = '1' THEN

IF (present_state = Reset ) THEN

ELSE

ELSE

ELSE

FLSE

ELSE

future_state <= Reset;

future_state <= present_state; -- count disable END IF;

END PROCESS CC1:

--- CC2: combinational circuit for calculating extra outputs

TC2 <= '1' WHEN ((present_state = Max_count)AND CE = '1') ELSE '0'; --terminal count

END FSM_like;

```

Fig. 36 Schematic of multiplier

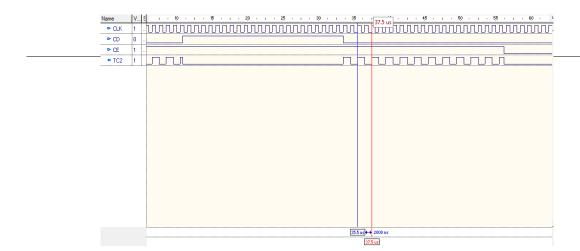

In the Fig. 37 we have the simulation.

Fig. 37 Simulation frequency divider by 2

In the simulation we check that every two clock's we have a pulse in output. To finish we are doing a T-Flip-Flop.

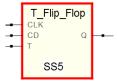

#### **1.3.2.2.4** The T\_Flip\_Flop

Finally we are doing a T-Flip-Flop that we can see in Fig. 38

Fig. 38 Schematic of T-Flip-Flop

The code of this block is in Fig. 39

```

LIBRARY ieee;

USE IEEE.STD_LOGIC_1164.all;

USE IEEE.STD_LOGIC_UNSIGNED.all;

ENTITY T_Flip_Flop IS

Port ( CIK

CD

END T_Flip_Flop;

-- Internal desciption in FSM style

ARCHITECTURE FSM_like OF T_Flip_Flop IS

CONSTANT Reset : STD_LOGIC := '0';

-- Internal wires

SIGNAL present_state, future_state: STD_LOGIC := Reset;

-- This thing of initialising these signals to the "Reset" state,

-- is only an issue for the functional simulator. Once the circuit

-- is synthesised, this thing is completely irrelevant.

-- reset counter

FISIF (CLK'EVENT and CLK = '1') THEN

END IF;

END IF;

-- reset counter

-- Synchronous register (D-type flip-flop)

END PROCESS state_register;

CS_1: PROCESS (present_state, T)

BEGIN

IF T = '1' THEN

tree future_state <= NOT (present_state);

future_state <= present_state;

END IF;

CS_2: combinational system for calculating extra outputs Q <= present_state;

END FSM_like;

```

Fig. 39 Code in VHDL of T-Flip-Flop

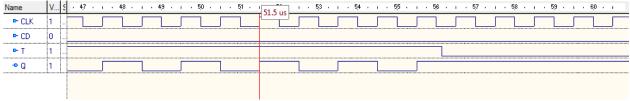

We see the simulation in the Fig. 40 and we check the proper operation.

Fig. 40 Simulation T-FF

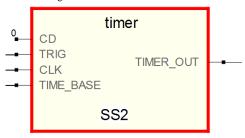

#### **1.3.2.3** The Timer

Now we are study the timer that we see in Fig. 41.

Fig. 41 Schematic of Timer

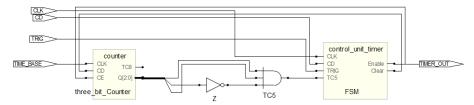

In Fig. 42 we have the code of this timer and we can see that this block has two blocks inside: the control timer and a counter.

Fig. 42 Code in VHDL of Timer

Inside this timer we have two blocks: a counter and a control unit timer that we can see in Fig. 43.

Fig. 43 Schematic inside of Timer

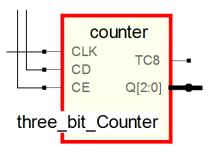

## **1.3.2.3.1** The Counter

We will perform a counter to eight as show in Fig. 44.

Fig. 44 Schematic of counter

In the code of Fig. 45 we can see that the counter goes from 0 to 7 depending the value of CE.

```

LIBRARY ieee;

USE IEEE.STD_LOGIC_1164.all;

USE IEEE.STD_LOGIC_ARITH.all;

USE IEEE.STD_LOGIC_UNSIGNED.all;

ENTITY counter IS

Port ( CIK : IN STD_LOGIC; CD : IN STD_LOGIC; CC : IN STD_LOGIC; CC : IN STD_LOGIC; CC : OUT STD_LOGIC; CC : OUT STD_LOGIC_VECTOR(2 DOWNTO 0); CC : OUT STD

END counter;

-- Internal description in FSM style

ARCHITECTURE FSM_like OF counter IS

-- State signals declaration

-- Constants for special states (the first and the last state)

CONSTANT Reset: State_type: Nua0; -- The first state. This is another name for the state Nua0

CONSTANT Max_count: State_type: Nua0; -- The last state. This is another way to name the state Nua7

---- State Register: the only clocked block

state_register: PROCESS (CD,CLK)

BEGIN

END PROCESS state_register;

--- CC1: Combinational system for calculating next state

CC_1: PROCESS (present_state, CE)

BEGIN

IF CE = '0' THEN future_state <= present_state; -- count disable -- just a simple state up count

future_state <= present_state; -- cour -- just

CASE present_state IS

VHEN Nun0 =>

future_state <= Nun1;

VHEN Nun2 =>

future_state <= Nun2;

VHEN Nun3 =>

VHEN Nun3 =>

future_state <= Nun4;

VHEN Nun4 =>

future_state <= Nun4;

VHEN Nun4 =>

VHEN Nun4 =>

future_state <= Nun6;

VHEN Nun4 =>

future_state <= Nun6;

VHEN Nun6 =>

future_state <= Nun7;

VHEN Nun6 =>

future_state <= Nun7;

VHEN Nun6 =>

future_state <= Nun7;

VHEN Nun7 =>

VHEN Nun7 =>

future_state <= Nun0;

END CASE;

END IF;

END PROCESS CC_1;

CC_2: PROCESS (present_state, CE)

BEGIN

-- The terainal count output

If ((present_state = Max_count) AND (CE = '1') ) THEN

TCS <= '1';

TC8 <= '0';

END IF;

END IF;

-- And now just copying the present state to the output:

CASE present_state IS

UHEN Num1 => "000";

WHEN Num1 => "001";

WHEN Num2 => "010";

WHEN Num3 => "011";

WHEN Num4 => "100";

WHEN Num5 => "011";

WHEN Num7 == "111";

END CASE ;

END PROCESS CC_2;

END FSM_like;

```

Fig. 45 Code in VHDL of counter

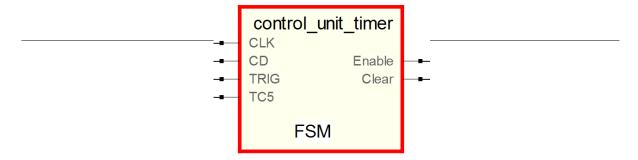

#### 1.3.2.3.2 The Control Unit Timer

Fig. 46 Schematic of control unit timer

In Fig. 46 we have the control unit timer. In the code of the control unit timer (Fig. 47) we can see that depending the inputs (if we are in case idle, clear\_s or count) we will have different values in outputs enable and clear.

```

ENTITY control_unit_timer IS

Port ( CLK

CD

TRIG

TCS

Enable

CLear

END control_unit_timer;

-- Internal desciption in FSM style

ARCHITECTURE FSM_like OF control_unit_timer IS

-- Internal wires

TYPE State_type IS (Idle, Clear_s, Count);

-> This is important specifying to the synthesiser the code for the states ATTRIBUTE syn_enum_encoding : STRING;

ATTRIBUTE syn_enum_encoding OF State_type : TYPE IS "sequential";

-- (It may be: "sequential" ("binary); "gray"; "gray"; "one-hot", etc.

SIGNAL present_state, future_state : State_type :

-- Constants for special states (the first and the last state)

CONSTANT Reset : State_type := Idle: -- The first state. This is another name for the state Idle

CONSTANT Max_count : State_type := Count; -- The last state. This is another way to name the state Count

State Register: the only clocked block.

The "memory" of the system (future events will depend on past events state_register: PROCESS (CD.CIK)

BEGIN

- reset counter

present_state (* Reset;

ELSIF (CIK'EVENT and CIK = '1') THEN - Synchronous register (D-type flip-flop)

present_state (* future_state;

END IF;

END PROCESS state register:

CC_1: PROCESS (present_state, TRIG, TCS)

BEGIN

CC_CT: PROCESS (present_state, TRIG, TCS)

CASE present_state IS

WHEN Idle =>

IF TRIG = '0' THEN

future_state <= present_state;

future_state <= Clear_s;

WHEN Clear_s =>

future_state <= Clear_s;

WHEN Clear_s =>

Future_state <= Count ;

WHEN Count =>

IF TC5='0' THEN

unt =>

IF TC5='0' THEN

future_state <= present_state;

ELSE

future_state <= Idle ;

END CASE;

END PROCESS CC_1;

CC_2: PROCESS (present_state)

BEGIN

CC_2: PROCESS (present_state)

BEGIN

The terminal count output:

CASE present_state IS

Clear (= "0";

WHEN Clear, s =>

Clear (= "0";

WHEN COUNT (STANDER)

CLEAR (= "1";

WHEN COUNT (STANDER)

CREAT (= "1";

CREAT (= "1";

CREAT (= "0";

CREAT

END PROCESS CC_2;

END FSM_like;

```

Fig. 47 Code in VHDL of Control Unit Timer

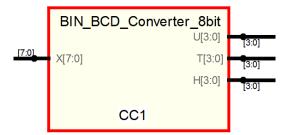

## 1.3.2.4 The Binary to BCD converter of 8 bit

This block has for input a binary number of 8 bits and the outputs are this number converted to BCD in units, tens and hundreds. For do this we need another block, it is the binary to BCD type 74185.

$Fig.\ 48\ Schematic\ of\ Binary\ to\ BCD\ converter$

The code of the binary to BCD converter of 8 bit is in this Fig. 49

```

-- A sample design for building circuits cascading

-- basic blocks

-- A BIN_BCD_Converter_8bit

LIBRARY ieee;

USE IEEE.STD_LOGIC_1164.all;

ENTITY BIN_BCD_Converter_8bit IS

END BIN_BCD_Converter_8bit;

ARCHITECTURE estructura_en_cascada OF BIN_BCD_Converter_8bit IS

COMPONENT Bin_BCD_type74185 IS

in STD_LOGIC;

out STD_LOGIC_VECTOR(6 DOWNTO 1)

-- Signals

: STD_LOGIC_VECTOR (8 DOWNTO 0);

-- Instantiation of up to 3 basic 1-BIN-BCD:

adder_0 : Bin_BCD_type74185

PORT MAP (

END estructura_en_cascada

```

Fig. 49 Code in VHDL of binary to BCD converter

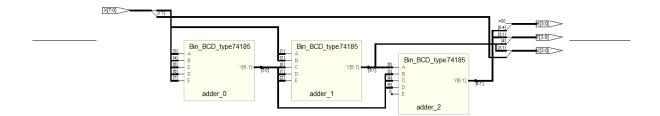

The circuit inside the binary to BCD converter is in Fig. 50. In this figure we can see the next block: the binary to BCD type 74185.

Fig. 50 Schematic inside the binary to BCD converter

## 1.3.2.4.1 The Binary to BCD type 74185

The code of this block is in Fig. 51. We can see the true table of this converter, the input of each block has 5 bits and in the outputs we have 6 bits.

Fig. 51 Code in VHDL of binary to BCD type 74185

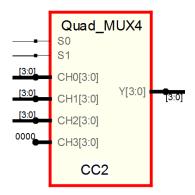

#### **1.3.2.5** The Quad\_Mux4

Fig. 52 Schematic of Quad Mux4

The code of the Quad\_Mux4 is in Fig. 53 and we can see a multiplexor that depending the values of S1 and S0, we have I output CH0, CH1, CH2 or CH3.

```

library isee:

use leee.std_logic_1164.all;

entity Quad_MUX4 is

FORT(

CH0 :IN STD_LOGIC_VECTOR(3 DOWNTO 0);

CH1 :IN STD_LOGIC_VECTOR(3 DOWNTO 0);

CH2 :IN STD_LOGIC_VECTOR(3 DOWNTO 0);

Y :OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

Y :OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

};

end Quad_MUX4;

architecture archMUX of Quad_MUX4 is

begin

Y <= CH0 UHEN SO-'0' AND SI-'0' ELSE

CH1 UHEN SO-'1' AND SI-'0' ELSE

CH2 UHEN SO-'0' AND SI-'1' ELSE

CH3 WHEN SO-'1' AND SI-'1' ELSE

CH3 WHEN SO-'1' AND SI-'1' ELSE

CH3 WHEN SO-'1' AND SI-'1';

end archMUX;

```

Fig. 53 Code in VHDL of Quad Mux4

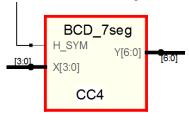

## 1.3.2.6 The BCD to 7 segments

Finally, to see the result we are going to convert of BCD to 7 segments.

Fig. 54 Schematic of BCD to 7seg

The code of the BCD to 7 segments is in Fig. 55.

```

- A sample design in which has to be programmed the functionality of: RBI_L, RBO_L i IT_L

- Make a project for this file.

- Add the functionality of the IT_L signal and synthesise again

- Add the functionality of the RBI_L signal and synthesise again

- Finely, add the output RBO_L and synthesise again

LIBRARY ieee;

USE IEEE.STD_LOGIC_1164.all;

ENTITY BCD_7seg IS

IN STD_LOGIC_VECTOR(3 DOWNTO 0);

IN STD_LOGIC;

OUT STD_LOGIC_VECTOR (6 DOWNTO 0)

END BCD_7seg;

-- EL vector d'entrada és: V_ENT(3) = D; V_ENT(2) = C; V_ENT(1) = B; V_ENT(0) = A;

-- EL vector de sortida és V_SOR(6) = a; V_SOR(5) = b; V_SOR(4) = c; V_SOR(3) = d; -- V_SOR(2) = e; V_SOR(2) = f; V_SOR(0) = g;

-- Descripció de l'arquitectura del bloc a partir de la TdV

ARCHITECTURE Arch_Taula_Veritat OF BCD_7seg IS BEGIN

("1101101");

WHEN "001:

WHEN "0100

("0110011");

VHEN "0110" =>

V <= ("1011011");

V =>

V == ("1011011");

VHEN "0111

"1110000");

WHEN "1000

VHEN "1001

VHEN "1011" = V <=

("1110011");

("1110111");

("0011111");

WHEN "1100

<= ("1001110");

WHEN "1101

END CASE;

ELSE Y <= ("0110111");

END IF;

END PROCESS:

END Arch_Taula_Veritat;

```

Fig. 55 Schematic of multiplier

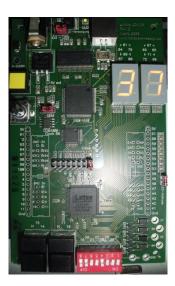

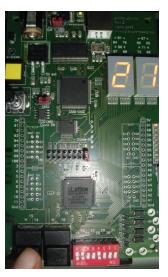

## 1.3.3 Total design

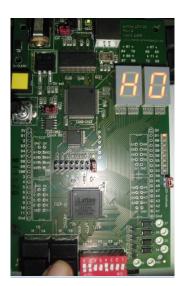

For show the result of this design, we can see in these figures the real result. In Fig. 56 we can see that we introduce a 3 and a 7 (the buttons we can see at the bottom); in Fig. 57 we pulse start and we can see the units and the tens of the result (and a led lights); and finally in Fig. 58 we pulse the other button for show the hundreds while the led is lit.

Fig. 56 Multiplier

Fig. 57 Multiplier

Fig. 58 Multiplier